Specification Automation for FPGAs

Today’s programmable devices require many of the same development techniques and tools as ASIC and full-custom designs, and the most sophisticated FPGAs fully qualify as SoCs. Your FPGA developers can benefit from the same specification automation solutions as their ASIC counterparts.

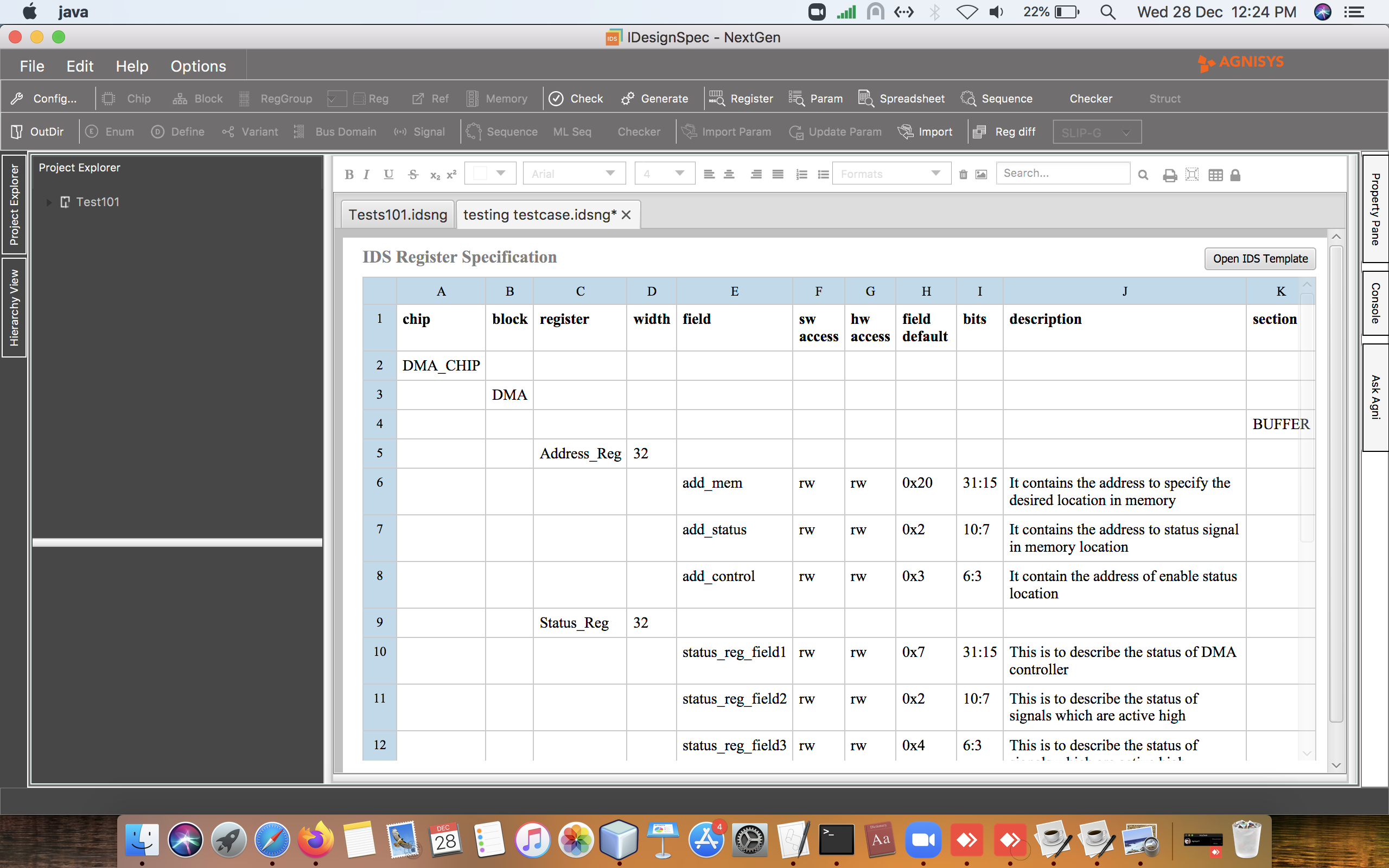

IDesignSpec GDI and IDS-Batch CLI Support for FPGAs

IDesignSpec GDI and IDS-Batch CLI include specialized support for your FPGA designers. IDesignSpec GDI and IDS-Batch CLI can read the specifications for pre-defined IP blocks provided by FPGA vendors for integration into larger designs. IDesignSpec GDI and IDS-Batch CLI generate UVM models, C/C++ headers, and documentation for these IP blocks automatically. They also generate target scripts for use in the FPGA vendor implementation tools. Agnisys directly partners with both Xilinx and Intel to support your team.

The IC Designer’s Guide to Automated Specification of Design, Verification, and Validation for Better Products

There are multiple causes for designs being wrong, but some of the most common are related to the design specifications and how they are distributed and maintained throughout the product development lifecycle. Learn how to address this issue by reading this guide.

Request a Discussion About Our Functional Safety Solution

There is no better way to appreciate the power of the IDesignSpec Suite of products than to see them in action. Schedule your discussion today.