SOC DESIGN

SoC Design

Developing a modern system-on-chip (SoC) device is challenging in many ways, but it starts with the design. Without a design, there’s nothing to verify, program, or validate. The design begins as a register-transfer-level (RTL) description, is transformed into gates and transistors by logic synthesis and layout tools, and is ultimately fabricated in silicon.

IT all Starts with IP

IDS-IPGen Provides Configurable and Customizable IP

IDS-IPGen Supports Custom IP

It is possible to imagine successful SoC using just a novel combination of commercial IP blocks, but that never happens. All chips contain at least some unique IP designed from scratch, and this is often the source of the biggest differentiation against competitors. Given the time and recourse constraints on SoC projects, designers are looking for help on custom IP as well as standard IP.

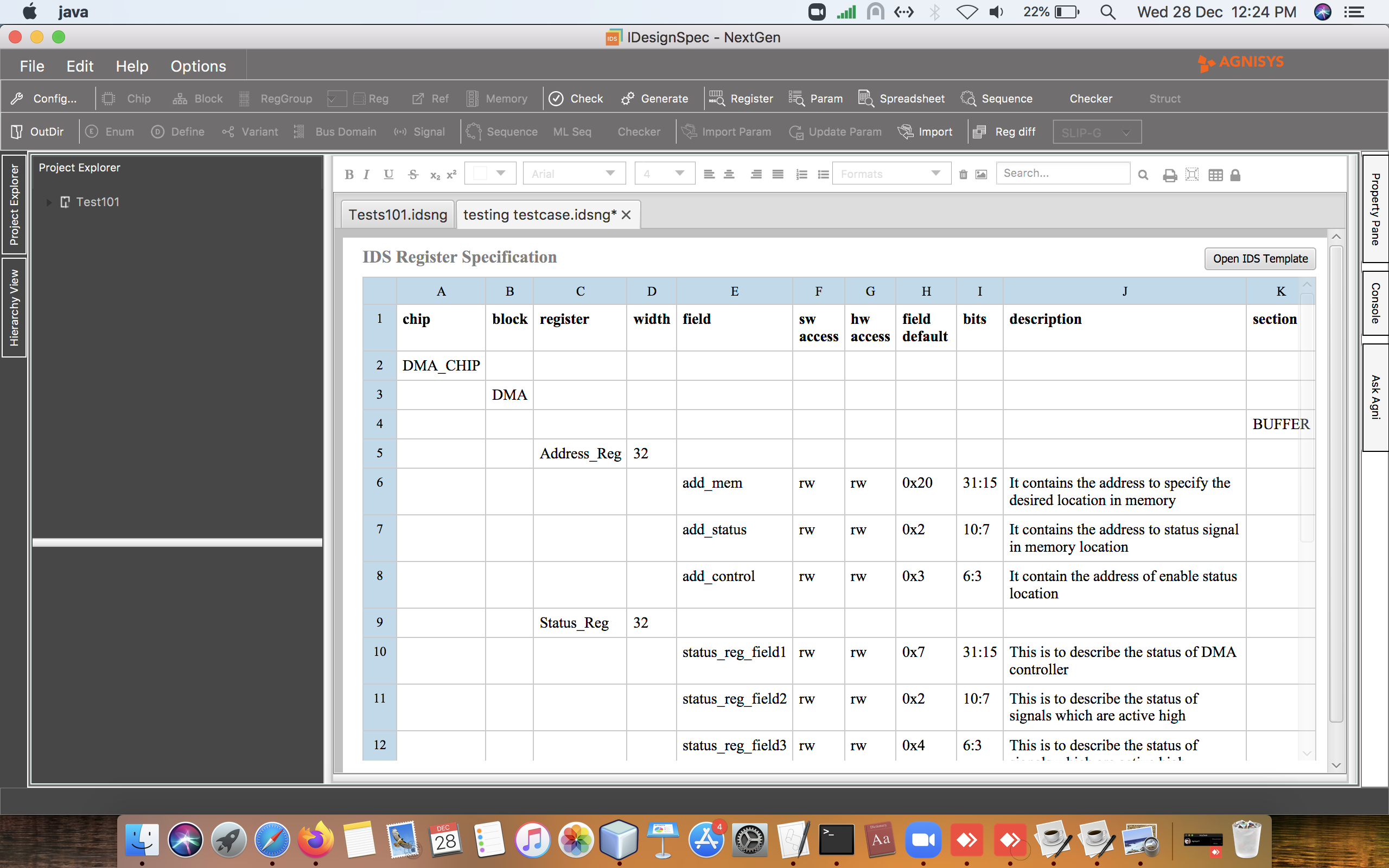

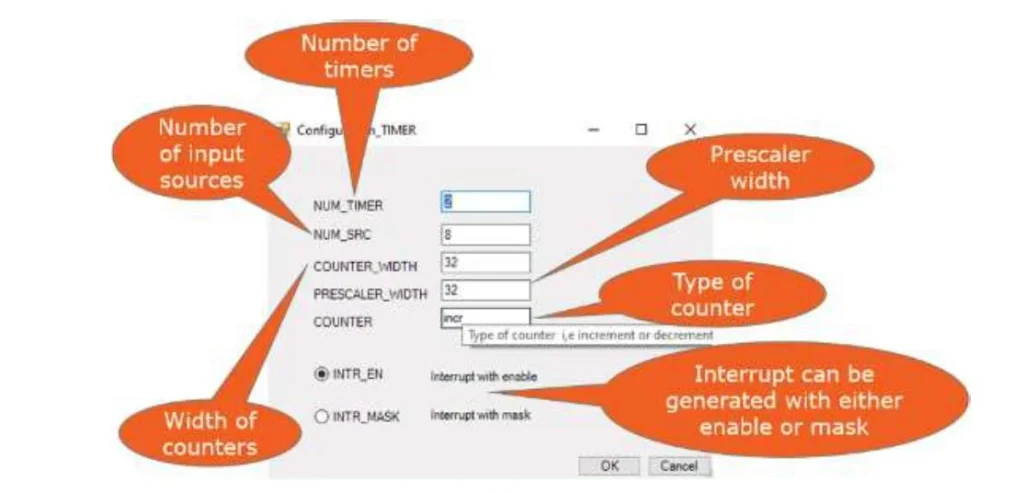

Agnisys provides a solution to this need. Even within novel block designs, there are many common elements that occur across many chips. Designers can generate finite state machines (FSMs) with IDS-IPGen, as well as registers and memories with IDesignSpec GDI and IDS-Batch CLI. These design elements are generated in RTL, ready for simulation and logic synthesis.

SoCs are hardware-software systems, and Agnisys provides help for programmers as well. In parallel with the RTL design, the IDesignSpec Suite generates the sequences necessary to configure and program the registers in the IP blocks. These sequences are provided in Universal Verification Methodology (UVM) form for verification and C/C++ code for validation and software development.

Hooking up IP Blocks Is a Pain

IDS-Integrate Automates SoC Hookup

Agnisys provides a solution for this challenge as well. IDS-Integrate™, also part of the IDesignSpec Suite, automates the process of integrating IP blocks together to assemble and generate complete top-level RTL designs. Designers use a simple but powerful specification format, including wildcards to deal with similarly named signals, to describe the desired interconnections.

For IP blocks with standard buses such as AHB and APB, IDS-Integrate automatically generates RTL aggregators, bridges, and multiplexors as required to satisfy the interconnection specification. For example, AHB interfaces on two IP blocks can be aggregated into a single bus. If the design includes IP using the AHB system bus and IP with APB peripheral interfaces, IDS-Integrate automatically generates an AHB-to-APB bridge between the two buses.

Agnisys Automates SoC Design

To meet ever tighter TTM requirements for ever larger and more complex SoCs, designers can no longer write and interconnect all their RTL blocks by hand. Agnisys provides specification automation solutions that generate correct-by-construction RTL designs plus files to help with verification, validation, and software. The benefits of this automation are replicated every time that specifications change. The result is faster chip development with fewer resources and increased confidence.