Importance of SystemRDL and PSS in the SoC Life Cycle

SystemRDL (System Register Description Language) plays an important role in the life cycle of System-on-Chip (SoC) development, facilitating efficient design, verification, and documentation processes. As SoC development is getting more complex day by day, with a huge number of components and functionalities integrated onto a single chip, managing registers becomes a significant challenge. SystemRDL addresses this challenge by providing a standardized language for describing and managing registers, offering various benefits throughout the SoC development life cycle.

Specification and Design

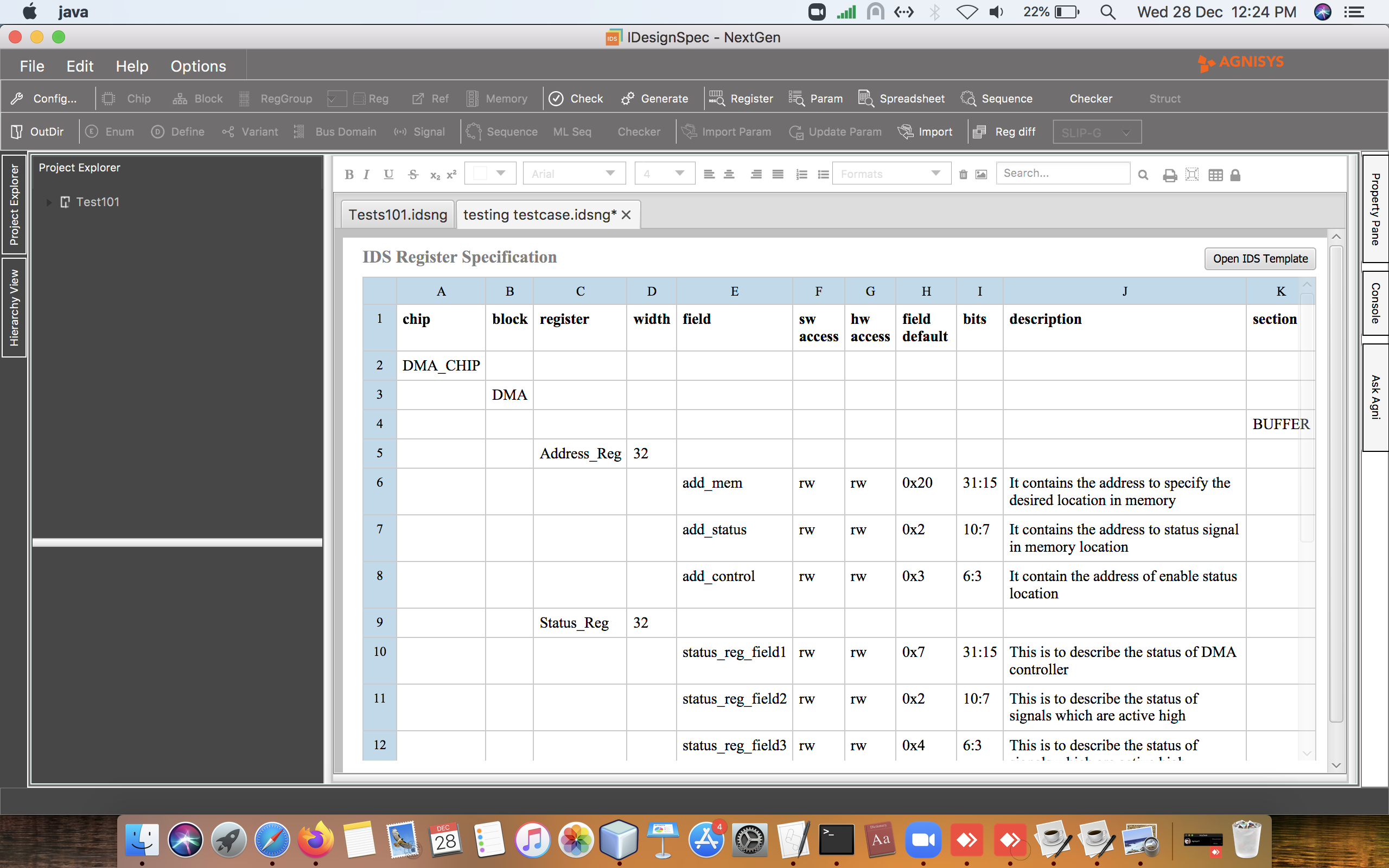

During the specification and design phase of a SoC project, SystemRDL allows designers to define the register map architecture comprehensively. This includes specifying the address space, register attributes, fields, access policies, and other relevant properties. By using SystemRDL, designers can create a clear and concise register specification that will act as a blueprint for the entire design process.

Verification and Validation

SystemRDL facilitates the verification and validation of register functionality through its integration with hardware description languages (HDLs) and verification environments. By generating register abstraction layer (RAL) models directly from the SystemRDL specification, verification engineers can perform extensive functional verification, ensuring that the registers operate correctly under various conditions and scenarios. Moreover, SystemRDL enables the creation of self-checking testbenches and automated verification scripts, streamlining the verification process and reducing the chances of errors.

Special registers, such as interrupt, control, and alias registers, are handled with specific attention to their unique characteristics and requirements. SystemRDL allows precise modeling of these special registers by specifying their attributes, behaviors, and access types within the specification. During verification, these attributes are rigorously tested to ensure that special registers respond correctly to read and write operations, initialize properly, and handle edge cases effectively.

Software Development

SystemRDL also plays a crucial role in software development, particularly in the context of device driver development, embedded programming, and software validation. By providing a precise description of the register interface, SystemRDL enables software developers to efficiently access and manipulate registers through device drivers and application software. Additionally, SystemRDL-based register models can be used in simulation environments to validate software behavior and ensure compatibility with the underlying hardware.

SystemRDL focuses on defining and verifying the characteristics of registers but does not cover how to program them. This gap is filled by using the Portable Stimulus Standard (PSS) and various graphical user interface (GUI) tools. PSS provides a standardized way to describe and automate test scenarios for register programming, ensuring thorough and efficient verification. GUI tools offer an easy-to-use visual interface for managing and configuring registers, making the programming process simpler.

Documentation and Maintenance

Throughout the SoC life cycle, SystemRDL serves as a central source of register documentation. The register specification encoded in SystemRDL enables designers, verification engineers, and software developers to understand the register architecture and its associated functionalities. SystemRDL facilitates register maintenance and updates by allowing designers to modify the register specification as needed and automatically propagate these changes across the entire design and verification environment.

How does IDesignSpec help in SoC development with SystemRDL?

Agnisys IDesignSpec™ Suite is an advanced EDA solution that empowers SoC developers with powerful features for seamless development of an SoC. Users can effortlessly transform their SystemRDL designs into HDL languages and other formats required for SoC development.

IDesignSpec Solution Suite

IDesignSpec GDI

simplifies digital system development with an easy-to-use GUI, aiding in managing registers and other components. It automates designing of registers, documentation, and verification, and integrates seamlessly into your design workflow.

IDS-Batch

IDS-Batch™ CLI is a tool designed for automating tasks in digital system development. It enables users to create and execute register specifications to perform various actions such as generating register RTL design, creating documentation, and many more things. This automation streamlines workflow processes, enhancing productivity and maintaining consistency in development tasks.

IDS-Verify

IDS-Verify™ is a tool for verifying the functionality and correctness of hardware designs. One of its key features is the use of SystemRDL as the specification input format. SystemRDL is crucial because it provides a standardized and efficient way to describe hardware registers, enabling IDS-Verify to automate the process of creating testbenches that stimulate the hardware with specific inputs and ensure the outputs match expected behavior. This helps designers simulate and debug their designs efficiently, ensuring they meet specifications.

IDS-Integrate

IDS-Integrate™ is a tool used in digital system development to streamline the integration of various design components and IP blocks. It helps automate the process of combining different modules, ensuring compatibility and consistency throughout the system. IDS-Integrate facilitates the integration of third-party IP, custom modules, and legacy designs into a cohesive system, reducing errors and accelerating the development process.

IDS-Validate

IDS-Validate™ is a tool used in digital system development to ensure the correctness and functionality of SoC designs. It automates validation processes by conducting comprehensive checks against design specifications and requirements. IDS-Validate helps detect errors, inconsistencies, and potential issues early in the development cycle, minimizing the risk of costly errors later on.It also helps users capture programming and testing sequences using PSS and various GUI-based options. This feature allows efficient design flows, simplifying the development process and reducing the potential for errors. With PSS and the IDesignSpec GDI GUI-based options, users can visually manage and streamline their projects, enhancing overall productivity and ensuring more accurate outcomes.

IDS-IPGen

IDS-IPGen™ is an innovative tool designed for high-performance IP/SoC teams who want to avoid the manual, time-consuming process of creating designs. This tool enables users to create “executable specifications” for designs and automatically generates RTL, a UVM-based verification environment, and tests. By automating these processes, IDS-IPGen significantly reduces development time and enhances productivity. It ensures accuracy and consistency in the design flow, allowing teams to focus more on innovation and less on repetitive tasks.

IDesignSpec not only supports native SystemRDL properties but also offers a range of proprietary properties to enhance the development process. It generates Verilog, VHDL, SystemVerilog, and UVM for design and verification tasks, plus C headers, HTML, PDF, and more. IDesignSpec also offers a SystemRDL compiler integrated within it. IDesignSpec is a complete package for streamlining the entire SoC development life cycle.

Conclusion

In summary, SystemRDL plays a very important role in the SoC lifecycle, offering a standardized and effective method for describing and validating registers. By capturing the hardware software interface (HSI) in SystemRDL and PSS, a single golden truth is maintained in every stage of development. SoC designers and engineers can enhance design processes, boost efficiency, and guarantee the effectiveness of their end products. As SoCs advance in complexity and integration, SystemRDL stands as an asset for ensuring successful SoC development and implementation.

Moreover, with Agnisys expertise and innovative tools alongside SystemRDL’s capabilities, developers can navigate the SoC design with greater ease and efficiency. IDesignSpec promises to streamline workflows, accelerate development cycles, and ultimately drive the creation of more robust and high -performance SoC solutions.