Vivado Support with IDesignSpec Suite

IDesignSpecTM (IDS) is a product suite that improves the productivity of FPGA/ASIC, IP/SoC, and system development teams. These products encompass an innovative register information management system to capture hardware functional specifications and addressable register specifications in a single executable specification. All downstream code and documentation for the addressable registers, sequences, or interrupts can be generated from this single specification along with validation in Xilinx Vivado Environment.

Vivado is a tool developed by Xilinx for creating digital designs. Vivado facilitates developers checking their designed RTL correctness and validating it in a hardware platform with different vendor’s boards containing Xilinx FPGAs. Currently, Zynq7000 family is used like Artix-7, Kintex-7 etc.. These special devices have two parts, the Programmable Logic (PL) block and the Processing System (PS) block. PL is used to implement RTL and PS is used for embedded applications oriented to ARM processors using Embedded C.

The following problems can be solved by IDesignSpec when generating outputs for Vivado:

- Simplified RTL implementation:

- Users do not need to worry about the RTL implementation. IDS takes care of generating the necessary RTL code.

- Pre-validated RTL:

- Users do not need to validate the RTL at their end because the IDS-generated RTL is already validated.

The following process achieves these results.

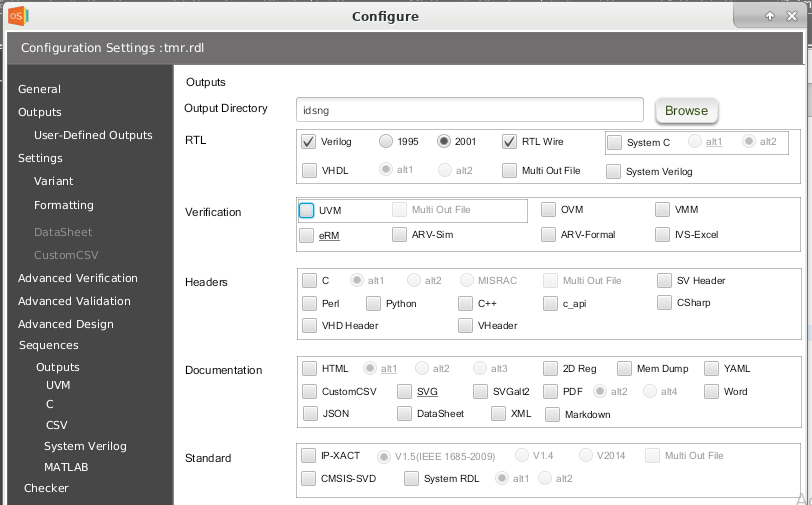

As shown in Figure 1 below, RTL output can be generated by the Agnisys cross platform GUI by going to the configuration window and selecting the desired output:

Figure 1: Configuration Setting in IDS

Users can generate the following two files from IDesignSpec:

- RTL output file

- AXI widget file

Flow of Process Execution:

This process is divided into two parts:

- Create package IP

- Generate bitstream with Zynq Processing System

Create Package IP:

The process to create package IP is shown below

Generate Bitstream:

Generate the bitstream with Zynq Processing System as shown below:

The generated bitstream is used to program the FPGA and run on the hardware. Vivado is built with an SDK for running projects based on C applications.

Application Example:

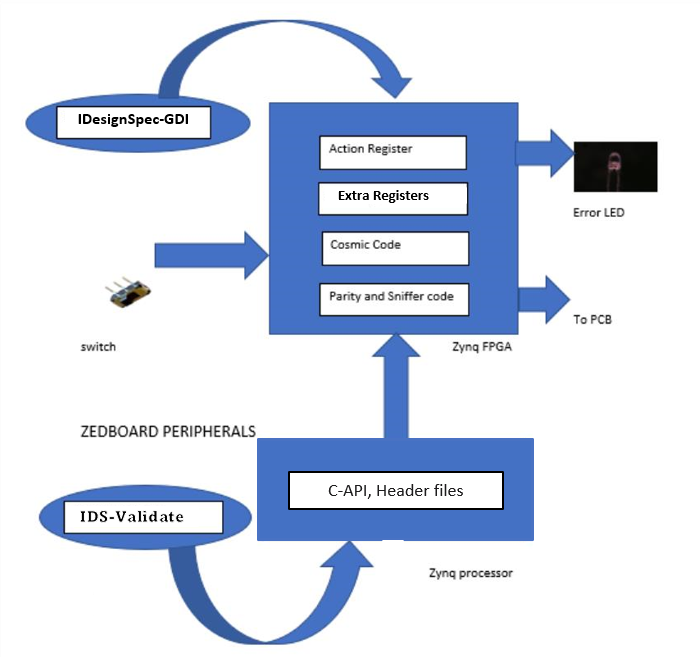

A typical application on the hardware platform, Zedboard, using both Vivado and SDK with IDesignSpec-GDI and IDS-Validate is shown below:

- Action register, extra register, parity, and sniffer code are generated by IDS.

- Cosmic code, which is hard-coded, will induce errors in registers through the switch.

- Parity and sniffer will detect errors in registers and send a signal to an error LED. This is part of the Vivado implementation.

- IDS-Validate generated C files are executed by the Zynq Processor through the Software AXI Interface, sending signals to the PCB according to the application. This is part of the SDK.

Conclusion:

With the help of the IDesignSpec Suite, users can create embedded projects very easily. There is no burden of writing HDL files and C programs for specific application projects.

Call for action: To get more information about how we can help you to create Vivado-based projects reach out here.