Automating IP Design and Verification

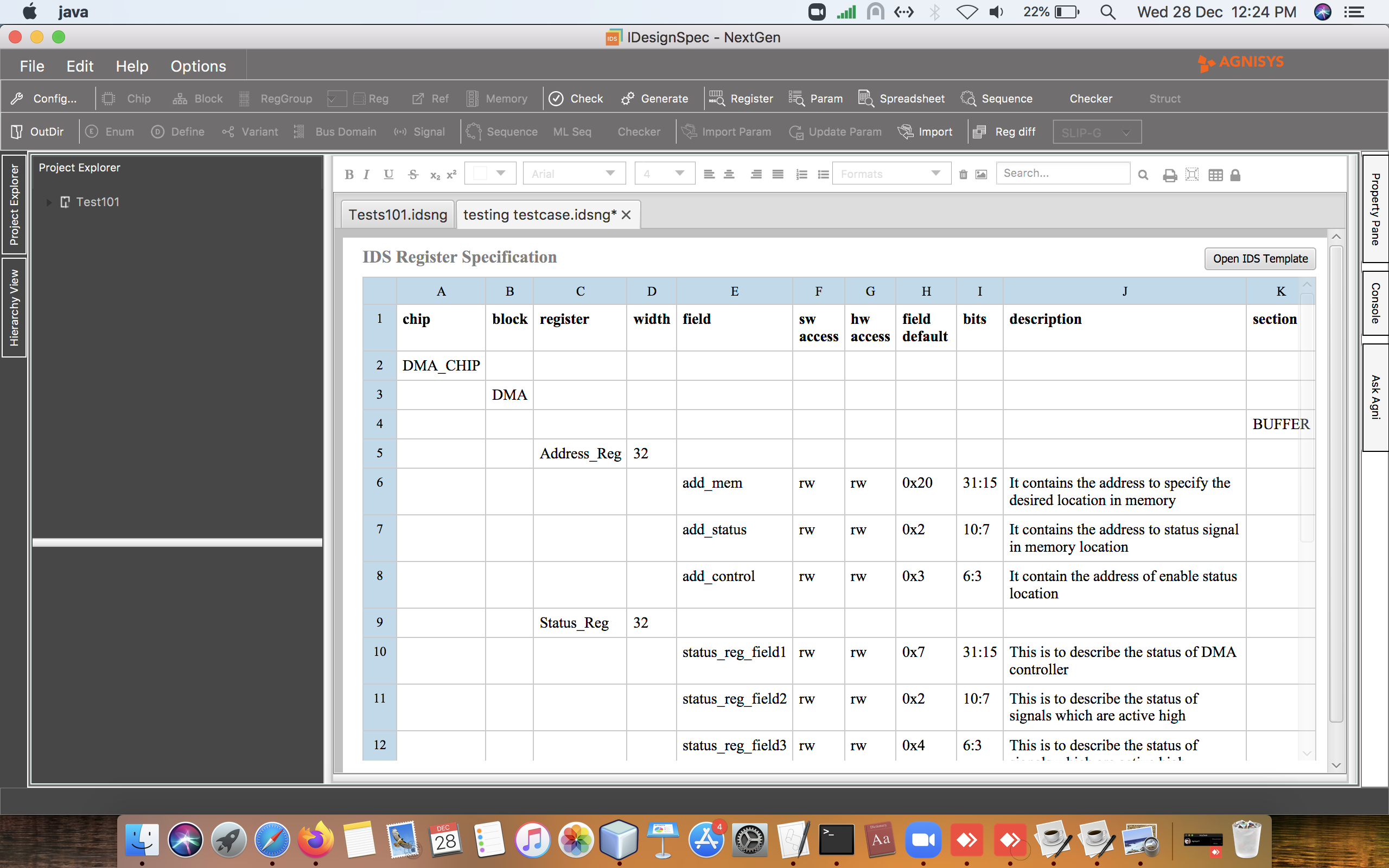

In my last post, I mentioned the three products we announced at the virtual Design Automation Conference (DAC) this year: IDS-Integarte™ (IDS-Integrate), Standard Library of IP Generators (IDS-IPGen™), and IDS NextGen™ (IDS-NG) ™. I’ve already blogged in detail about IDS-Integrate, so for today I’m focusing on IDS-IPGen. This library is an extension to our product line that leverages our extensive experience in automating registers and sequences to provide more value for our customers.

It’s no surprise to anyone that design reuse plays a big role in today’s huge system-on-chip (SoC) projects. It’s impractical for any team to design and verify many millions of gates from scratch, so IP from different sources helps to make large SoCs feasible with smaller teams and accelerated schedules. Internal reuse from previous projects is almost universal, but over the past 25 years or so commercial IP has grown tremendously in value and importance. Instantiating a well-proven design block saves valuable time and resources while reducing verification effort.

Some would argue that the most savings and the safest results are obtained when using IP that exactly matches a block already included in production silicon. However, it is rare for any two chip projects to have precisely the same requirements for an IP block. User-specified configuration options are required for many kinds of IP, and deeper customization such as adding a unique instruction to a RISC-V processor are also highly valuable. Options and customization must be built into a commercial IP product. Users should not manually edit RTL files, which is inefficient, error-prone, and problematic when the IP vendor provides a new version with bug fixes or desirable new features.

Many successful IP products are created by generators, so users can change parameters and push a button to get a design block with different characteristics. Our IDS-IPGen library meets this description perfectly. It is not simply a library of IP; it is a library of IP generators with many configuration and customization options. We have General Purpose Input/Output (GPIO), I2C, timer, and programmable interrupt controller (PIC) IP available today. In addition, we have a direct memory access (DMA) engine and an Advanced Encryption Standard (AES) engine in development, with more IP to come prioritized by customer demand.

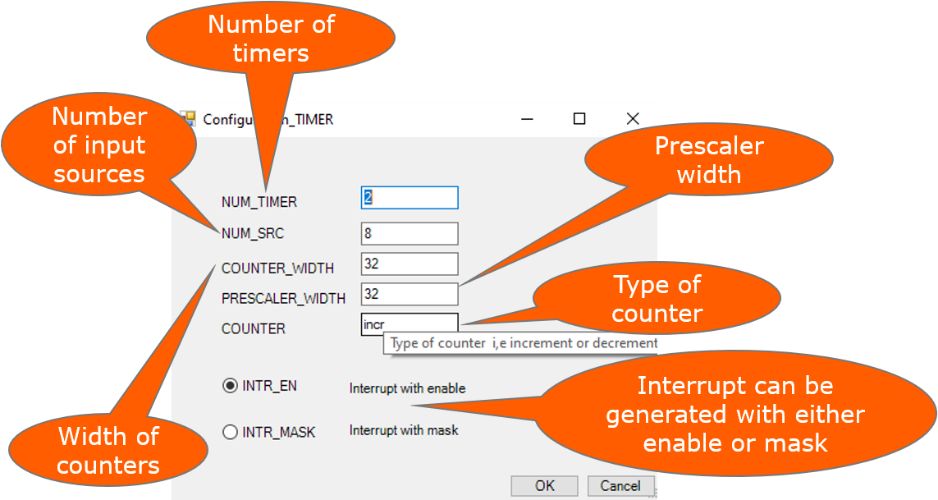

What sort of configuration options do our users have? For the GPIO standard interface, choices include the number of pins used by the interface, the number of input sources, and whether interrupts are generated with an enable or a mask. The simple I2C (also known as I2C) protocol IP has only a few parameters, but these are critical for sizing the IP correctly. Users can choose the size of data that is transferred in each transaction and the number of bits used to address slave device. Our timer block has more options, including number of timers, counter width, increment or decrement, and type of interrupt.

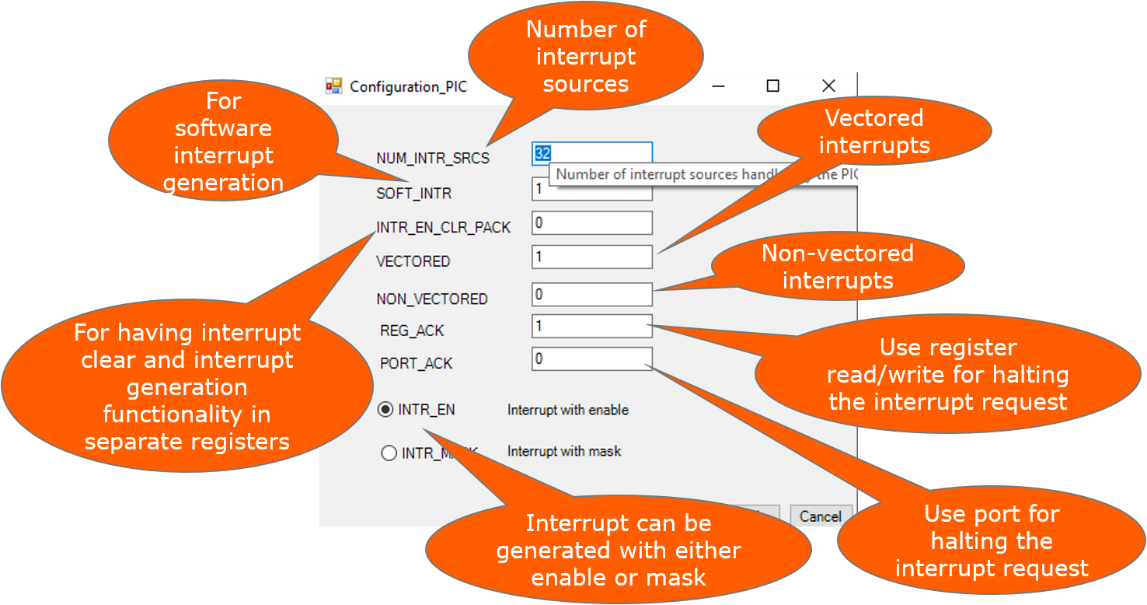

The PIC is our most complex and most configurable IP, supporting vectored and non-vectored interrupts, enable or mask interrupt generation, software-driven interrupts, and more. Beyond these top-level configuration options, we provide several other types of customization. Users can select from an array of popular on-chip buses for the “back side” of the interface IP. These include Wishbone, OCP, AMBA/AXI/AHB/APB, and even proprietary protocols. Users can specify their desired operating frequency and custom signals to be added. Every block in the IDS-IPGen library contains a set of registers for software control. We offer the flexibility to add custom fields to the registers and add custom registers for user-specified functionality.

Our IDS-IPGen generators output RTL code for the specified configurations, all ready for inclusion in chip-level verification and logic synthesis. But we provide much more than just the hardware design. Our documentation is so complete that it can be merged into internal chip specifications or even user manuals. IDS-IPGen also generates Universal Verification Methodology (UVM) models to help build the verification testbench. Therefore, we help the verification team as well as the hardware designers, and we even provide assistance for software engineers.

IDS-IPGen can generate a set of standard programming sequences to initialize and configure the registers of the selected IP blocks. These cover all the possible IP scenarios. Users access these sequences through customizable application programming interfaces (APIs). Programmers use these APIs as building blocks to configure and access the IP registers in verification and validation testbenches, bring-up tests running in the lab, and even production device drivers.

IDS-IPGen is not just another collection of reusable design blocks. We provide hardware reuse, verification reuse, documentation reuse, and programming sequence reuse. Our designs are extensively verified and validated. We’re excited to be in full production release for the first four elements in our IP library. We invite you to take a look and ask that you let us know what additional types of IP would be valuable to you. We’re proud to be able to help you create ever bigger SoCs without exploding your team sizes or project schedules.