DAC May Be Virtual, but Our New Products Are Not

Anyone who’s worked in the EDA industry, and many of its customers, are aware of the annual Design Automation Conference (DAC). This event dates back 57 years, a long time for anything to last in our high-tech world. It’s two shows in one: a competitive, peer-reviewed technical conference combined with a large vendor exhibition. We have been attending DAC since 2009 and have always found it to be a valuable experience. The technical program is stimulating, we get to check out what other vendors are doing, and we’re able to talk to many customers and prospective customers over just a few days.

Of course, this year is different. As for most other public events and shows, we can’t gather together physically at this time. Therefore, DAC 2020 is a virtual event, with the speakers delivering their talks and papers online and the vendors hosting virtual booths. Agnisys is participating as always and we are looking forward to engaging with all of you in a different but still personal way. The virtual booths are configured to enable real-time chats and schedule detailed discussions. We can’t meet face to face or shake hands, but we can listen to your chip design and verification challenges and suggest ways that we can help.

As part of our commitment to DAC, we have announced three major new products that will be our focus for the show. We have talked about some of these before, and have been working with early adopters to refine features and user experience. Now we are announcing general availability for all users of our Standard Library of IP Generators (IDS-IPGen™), IDS-Integrate™ (IDS-Integrate), and IDS NextGen™ (IDS-NG). We think that all three are exciting and important additions to our solutions and would like to share a few details.

While we are primarily an EDA company, we have always generated both design and verification IP from IDesignSpec™ for registers, expanding this capability for sequences with IDS-Validate™. With SLIP-G we take a significant step forward in our IP offerings. It provides an interface for IP customization and configuration and generates the design RTL, UVM testbench models, and programming sequences. We have GPIO, I2C, timer, and programmable interrupt controller (PIC) IP available today, with more to come prioritized by customer demand.

A modern system on chip (SoC) contains hundreds or thousands of blocks from multiple sources, including commercial IP, reused functionality, and new design. Assembling these into a complete chip is a big challenge. SoC Enterprise is a flexible and customizable environment for the design assembly of even the most complex chips. SoC-E can generate RTL aggregators, bridges, and multiplexors as needed by the SoC architecture, more additions to our IP portfolio. Our Smart Assembler technology automatically integrates and connects these blocks, SLIP-G IP, IP from other sources, and user blocks into a complete SoC.

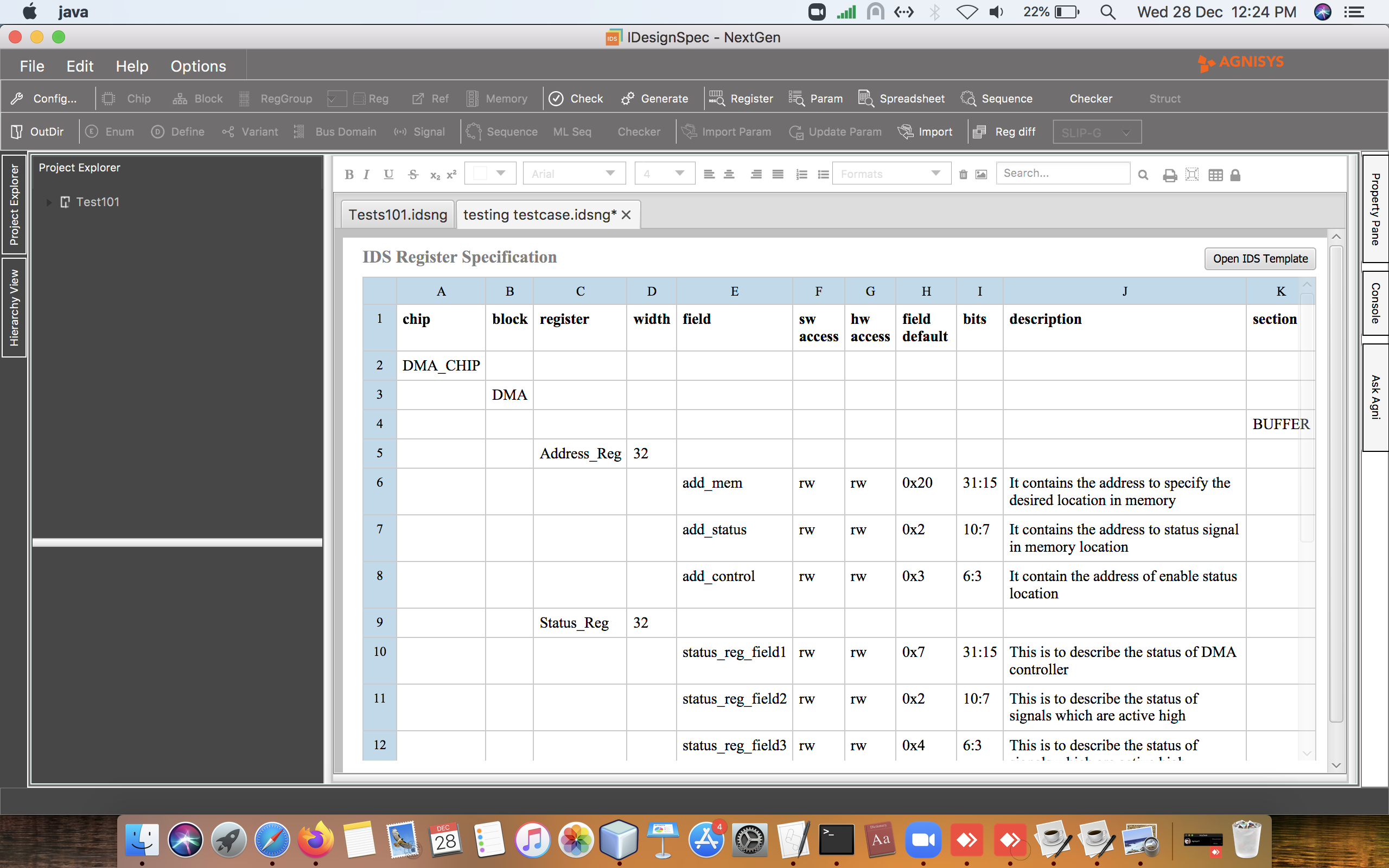

We also have a new common entry point for our design and verification flow. IDS NextGen™ is a specialized integrated development environment (IDE) for large IP blocks and SoCs. It includes a sophisticated GUI for capturing register and sequence specifications. It provides a common front end for IDS, ARV, ISS, and SoC-E, enabling a fully automated flow for registers and sequences. IDS-NG helps you increase your efficiency, improve your design and verification quality, reduce project costs, and minimize time to market.

These three new products, together with our existing solutions, deliver a complete flow from register and sequence specification to assembly, design, verification, and validation of complex SoCs, From a single specification, you can generate design RTL, complex programming, and test sequences, UVM testbench models for simulation, assertions for formal verification, C code for firmware and device driver development, comma-separated-value (CSV) files for Automatic Test Equipment (ATE) post-silicon validation, and user documentation in multiple formats. The Agnisys solution increases the productivity and work quality of individual engineers and project teams while eliminating system design and verification errors.

Furthermore, the inclusion of UVM IP and embedded system security considerations fortifies the solution’s capability to address the growing demand for secure and reliable embedded systems. This holistic approach empowers engineers and project teams, significantly enhancing productivity while mitigating system design and verification errors.

The Agnisys solution, augmented by PSS data modeling, SoC verification and testing, SOC validation, UVM IP, and embedded system security, stands as a comprehensive and integrated response to the multifaceted challenges of modern SoC development and validation.

We would love for you to join us virtually at DAC to learn more. The online exhibition is live from July 20 to July 22, and you can visit our virtual booth any time during this period. To register or find out more about the technical program and other aspects of the event, visit the main DAC site. We look forward to seeing you online!