Newsletter 2020 Q2 | Agnisys

In this newsletter, you will find articles about the basic differences between Paged registers and Alternate register, Auto-Mirroring for volatile registers, Clock Domain Crossing synchronization in IDesignSpec and smart assembly of SoC designs. Wish you and your families a safe and healthy future.

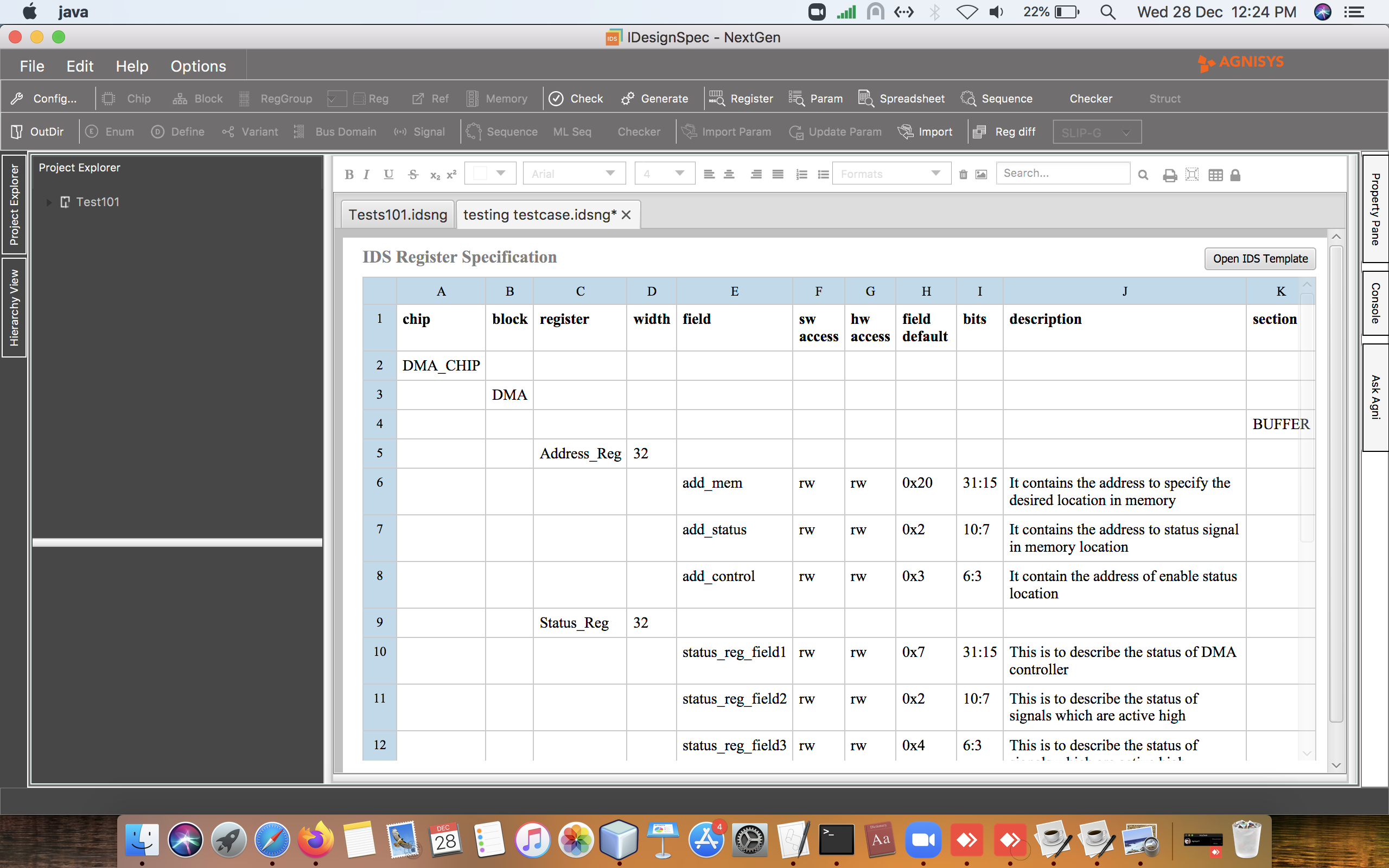

Auto-Mirroring for Volatile Registers

UVM Register Abstraction Layer (RAL) is a high-level object-oriented abstraction layer to access the registers in a design. The RAL model mimics the design registers and this allows the verification team to ensure correctness of the design. UVM RAL supports different register access like R/W, RO, WO, W1C, etc. from the CPU bus (we call it the software side). In addition, there is access from the application logic for which the design is being built (we call it the hardware side). The same model can be accessed by multiple software side buses. When a hardware event occurs in the design, the registers can be updated as a result. Such registers are called volatile registers. For example, a register can indicate the state of the application logic which is read by the CPU – hardware access is write-only, and software access is read-only. The value from the design (RTL) will not be mimicked on the RAL model on its own; something needs to be done. To overcome this shortcoming in the UVM RAL, we use a technique called auto-mirror. This article discusses how we handle it in IDesignSpec™. Read more

Support for CDC Synchronization in IDesignSpec

A typical SoC register block can be accessed from two sides. On one side, there is a register bus interface (we call it the software side) while on the other side, there are signals driven by the user’s application logic (we call it the hardware side). A register bus can be any industry standard parallel bus protocol like AMBA-AHB, AMBA-APB, AXI, Tilelink or serial buses like I2C or SPI. The register bus forms the SW interface while the signals driven from the user’s application logic form the HW interface. Read more

Difference between Paged & Alternate Registers

When creating a register map, sometimes designers need multiple definitions of a register as it appears to their logic. In IDesignSpec™ there are multiple ways to describe such registers, which can have multiple contexts. One possible way is to use paged registers, and another is to use alternate registers. In this article we will compare and contrast these two register types. Read more

Smart Assembly of SoC Designs

System-on-chip (SoC) projects are, by their very nature, complex and difficult to complete successfully. Specification, architecture, design, and verification are all challenging. Increasing demand for design functionality and design performance makes every step of the design process more difficult, even the seemingly simple task of assembling all the pieces that make up the SoC. Read more