Agnisys to Unveil Specta-AV at DAC 2019

BOSTON, MA – May 20, 2019 – Agnisys, Inc. to unveil Specta-AV™, a comprehensive UVM Testbench Generator for today’s IPs/SoCs, at the Design Automation Conference (DAC) June 3-5, 2019 in Las Vegas, NV.

Accellera’s Universal Verification Methodology (UVM) has become the de-facto verification methodology for today’s SoCs due to its reuse benefits and verification efficiency with constrained random stimulus and coverage-driven approach. However, power-users of UVM still have to manually write a massive amount of code in the range of multi-millions. Considering that manual creation is error-prone, this amount of code is staggering and consumes significant manpower.

While UVM is projected to increase its adoption growth for verifying new-generation SoCs for Machine Learning, Automotive, Vision, 5G, and IoT applications, its steep learning curve is difficult to surpass to yield production-level code. Automation of UVM creation is critical and will play a key role to support ongoing innovations in the aforementioned applications.

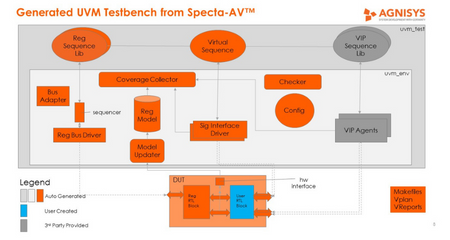

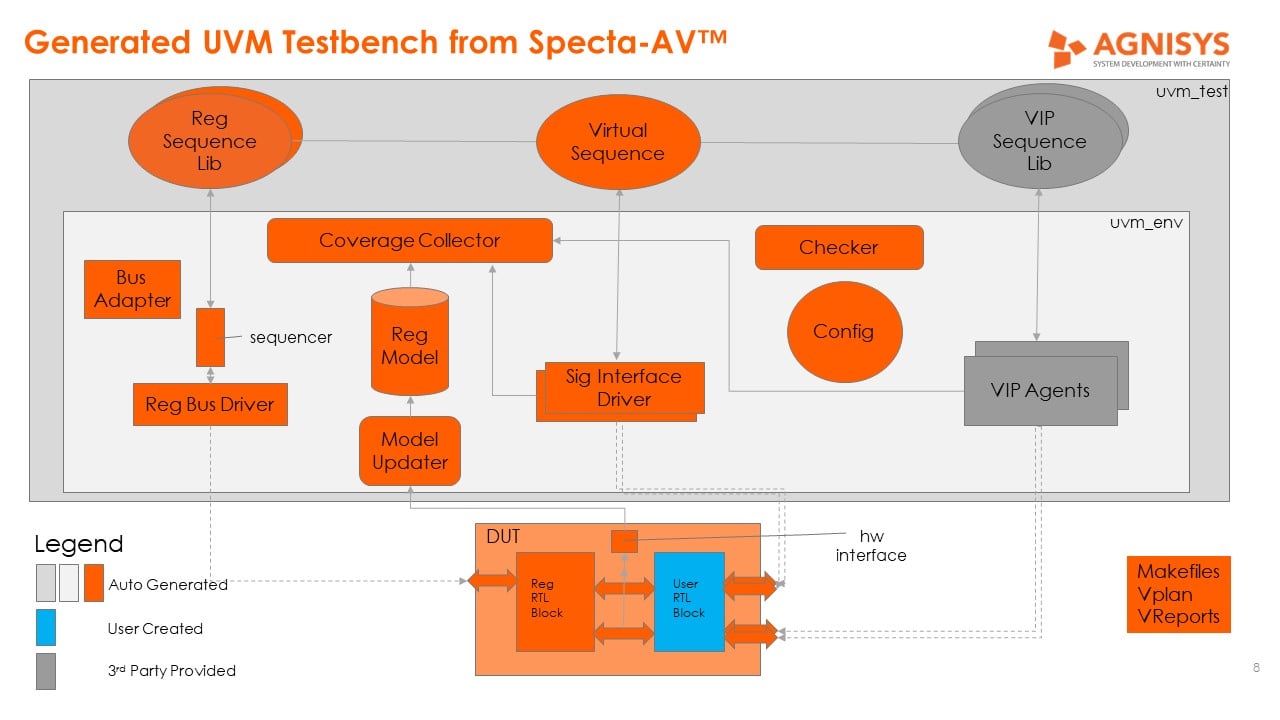

With Specta-AV, the generation of the complete UVM testbench architecture including sequence items, configurations, checkers, and coverage are all automated. Specta-AV generates code from a golden specification which synchronizes all design and verification activities. Changes in the specification only entails re-generation of the code which prevents any disconnect between SoC groups that can be a cause of SoC functional flaws and project delays.

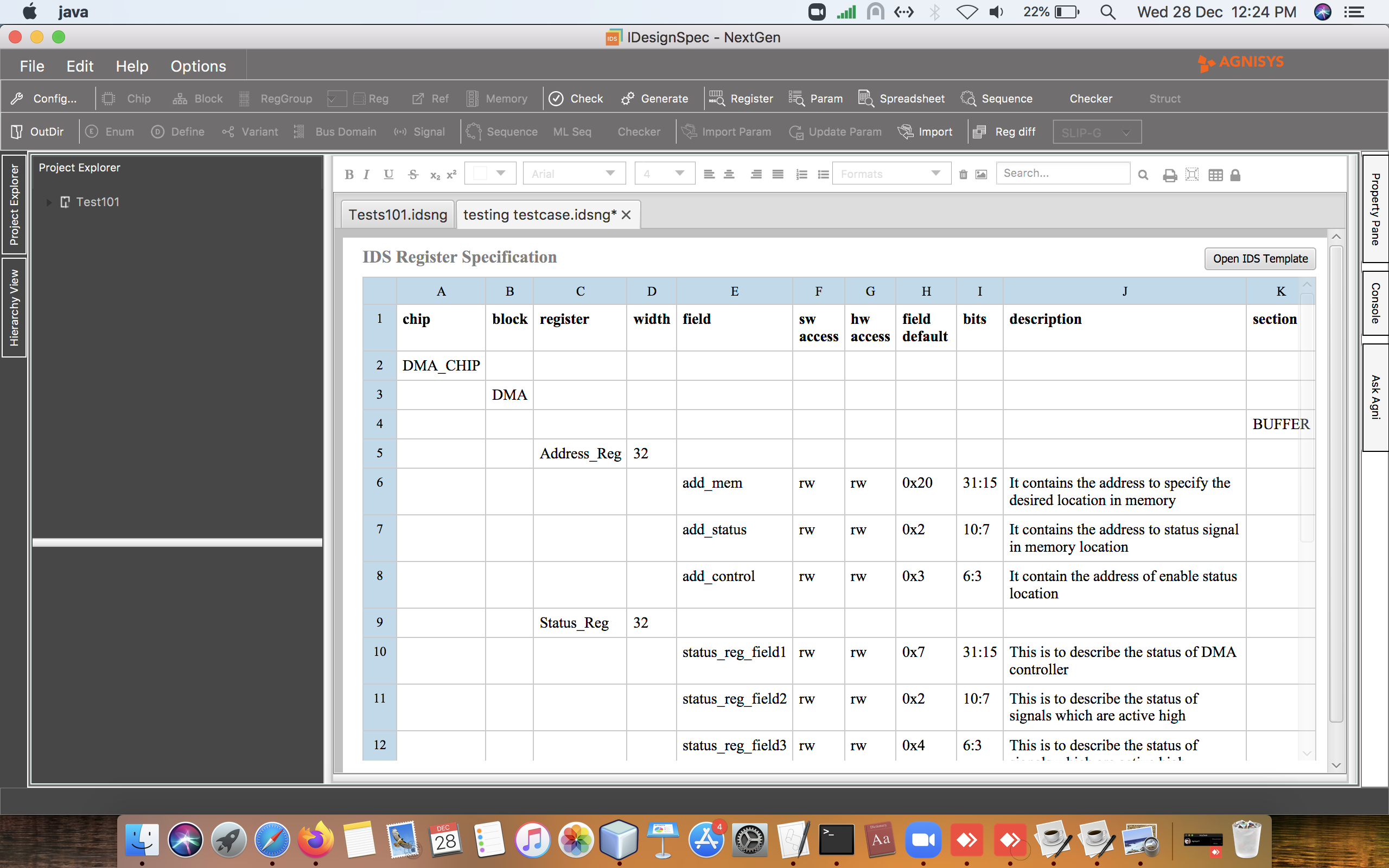

The power of the solution is built on the technology that can parse and generate code from a hierarchical register specification in IP-XACT, SystemRDL, Word, and Excel. Fundamental to IPs and SoCs are the register and memory maps, and the ability to exercise them is critical to the value a UVM testbench generator.

The tool flow consists of three main basic parts:

- The user specifies register and memory map definitions, functional and test sequences, UVM configurations, checkers, and interesting coverage.

- The user specifies commercial protocol VIPs and instantiates the DUT module.

- The user generates the following code:

- Register RTL, UVM model, C Headers, HTML

- Bus Interface Logic: AXI, APB, AHB, RISC-V TileLink

- UVM Environment, Sequences (C, SV-UVM, SystemC, PSS), Checkers, CoverGroups, Assertions

- Simulation Makefiles

- C-Based Tests for Firmware

- Post-Silicon Validation Tests

“UVM has reached maturity and is now ready for a fully-automated tool flow,” said Anupam Bakshi, Agnisys Founder and CEO. “With the current version of Specta-AV, we’re able to generate about 50-60% of the required UVM code to verify a full SoC. We have been building code generators since 2009 and Specta-AV is the pinnacle of our code generation technology. We will continue to build it to reach our vision where 100% of the required UVM code is automatically generated.”

A full demonstration of Specta-AV will be shown at DAC along with our latest complementary solutions that automate verification and help in minimizing SoC functional flaws.

Technical Sessions and Demos

June 3-5, 2019 from 10:00 AM to 6:00 PM at Booth #812

We invite DAC registered attendees to schedule an appointment at our booth or contact us to learn more.

The following presentations will be offered continuously at the Agnisys booth throughout the day. Attendees are invited to visit our free espresso bar and take our Design/Verification Quiz for a chance to win a wireless charger.

UVM Testbench Generator

With the ability to parse register specs and retarget sequences in C or SystemVerilog, the tool generates the entire UVM Testbench with sequence items, configurations, checkers, coverage and even the plumbing within UVM.

Cloud-Based Code Generator for Registers and Sequences

We are taking IDS NextGen™ to the cloud. This will revolutionize how the files are managed: no hassles in managing local files, no issues with storage and no local software installation required for the product.

Support for RISC-V TileLink Bus Protocol

TileLink is an open-source bus-protocol with low latency and cache-coherent shared memory designed for RISC-V, and it’s now supported in IDesignSpec.

Sequences in Python or NLP-based Sequence Detection

We now have come to a point where we can pick sequence of operations from a functional specification and create meaningful code from it.

Vertical Reuse of Registers and Sequences

We will discuss the underlying challenges and demonstrate best-practices on how to reuse the auto-generated register RTL, UVM model, UVM test environment and configuration/test sequences at subsystem and final system.

Register Design for Low-Power

In order for IoT devices to become as ubiquitous as we have envisioned it to be, low-power is one of the main requirements. IDesignSpec now supports several optimization techniques such as clock gating and hierarchical decode.

Requirements Traceability

IDesignSpec now supports traceability. The generated RTL code, UVM reg model and C headers now include a traceability tag from the functional spec. This is useful for safety-critical designs for automotive and avionics.

About Specta-AV

Specta-AV is a comprehensive UVM Testbench Generator that automates verification and validation with industry-proven code generation technology. With the ability to parse hierarchical register specification from IP-XACT, SystemRDL, Word or Excel, and the capability to retarget complex sequences into various modeling languages such as C and SystemVerilog, Specta-AV facilitates a methodology where multiple SoC groups can align and work from a golden specification for auto-generating UVM Tests/Environments/Agents, C-based Tests and Post-Silicon Validation Tests.

About Agnisys

Agnisys, Inc. is a leading supplier of Electronic Design Automation (EDA) software for solving complex design and verification problems for system development. Its products provide a common specification-driven development flow to describe registers and sequences for System-on-Chip (SoC) and intellectual property (IP) enabling faster design, verification, firmware, and validation. Based on patented technology and intuitive user interfaces, its products increase productivity and efficiency while eliminating system design and verification errors. Founded in 2007, Agnisys is based in Boston, Massachusetts with R&D centers in the United States and India. www.agnisys.com

Specta-AV™ is a trademark of Agnisys, Inc. All other trademarks cited herein are the property of their respective owners.

Media Contact: Louie De Luna, Agnisys Director of Marketing/Sales

Phone: +1 855-VERIFYY

Email: marcom@agnisys.com

Overcoming the weaknesses of traditional natural language specifications requires writing the specifications in a precise format rather than natural language, and making this format executable so that tools can generate as many files as possible for the design, verification, programming, validation, and documentation teams. Learn how Agnisys approaches a solution to this challenge that is available today.