shift_left (Validation Sequences) = Verification Sequences

Verification and Validation are two sides of the same coin

In 2011, Intel discovered a design flaw in its Sandy Bridge combination graphics-microprocessor chip that led to not only a major production delay but that ultimately cost more than $1 billion in replacement costs and lost revenue. If you’re searching for a clear-cut example as to why finding bugs early in the development process is always a top priority, look no farther than that. A product recall can be a terrible experience for everyone involved, but the costs associated with that recall alone are the stuff that nightmares are made of.

Yet at the same time, the complexity of the modern SoC environment has made things difficult in this regard to say the least. Getting SoC to market (and doing so with quality) is such an enormous task that teams are always looking for newer and more innovative ways to shorten the development time. The situation has also raised the requirement to incorporate verification and validation as a one-step process to catch bugs from an early design stage. Bringing the enormous tasks of verification and validation closer together is great news for the entire semiconductor industry.

This, however, is where the concept of “shift left” enters the conversation. As its name suggests, “shift left” is a series of activities and processes that better position design teams to anticipate and address downstream issues upfront, thus fixing a small problem now before it becomes a much bigger (and more expensive one) tomorrow. It’s the heart of the idea that you should “test early and often.” It also does so in a way that has proven to shorten development times so that no time is wasted late in the process where every second counts.

Why This Matters

But before we can focus on the importance of “shift left,” we must first address the early stages of this process in general. Verification and Validation are two critical steps in the creation of electronic systems, but over the last few years, in particular, their roles (and how those roles relate to one another) has changed.

In the modern era, there is an urgent need to enable users to describe the programming and test sequences of a device in a way that automatically generates sequences ready to use from an early design and verification stage, all the way up through post-silicon validation.

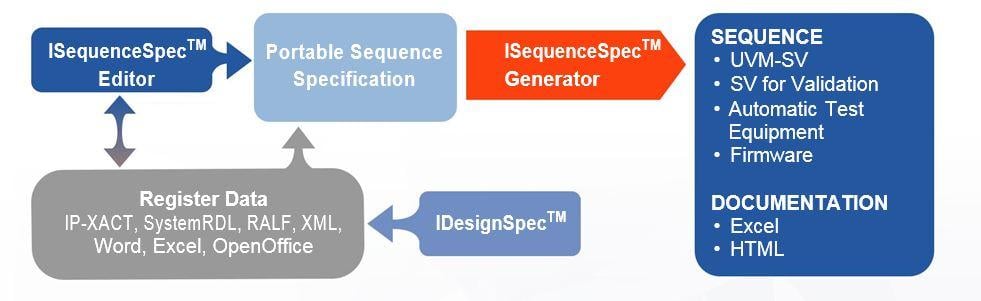

Using the principles at the heart of “shift left,” this process can now be combined into a single step process using just a portable sequence generator for verification, firmware and validation – all at the same time. IDS-Validate™ is one example of such a tool, which is intended to help design teams generate both the unified UVM sequences necessary from the specification to both catch bugs early and often and increase the ability for people to collaborate and communicate across teams.

Thanks to solutions like IDS-Validate, we are now seeing a major opportunity to end the perception that verification and validation are separate tasks for the vast majority of the chips that are currently being created. The fact that engineers can now write a single sequence specification and generate UVM sequences for verification, Verilog sequences for validation AND various output formats for the purposes of Automatic Test Equipment (ATE) is a massive time saver to say the least.

One of the major benefits of a single specification format is that a deeper level of synchronization is now a guarantee between various disparate stages of the development, from verification to post-silicon validation and everything in between. Not only are these test sequences automatically generated (allowing engineers to free up their valuable time to focus their efforts elsewhere), but it also provides invaluable insight that can be leveraged to fine-tune performance and to better understand complicated hardware/software interactions at a deeper level than ever before.

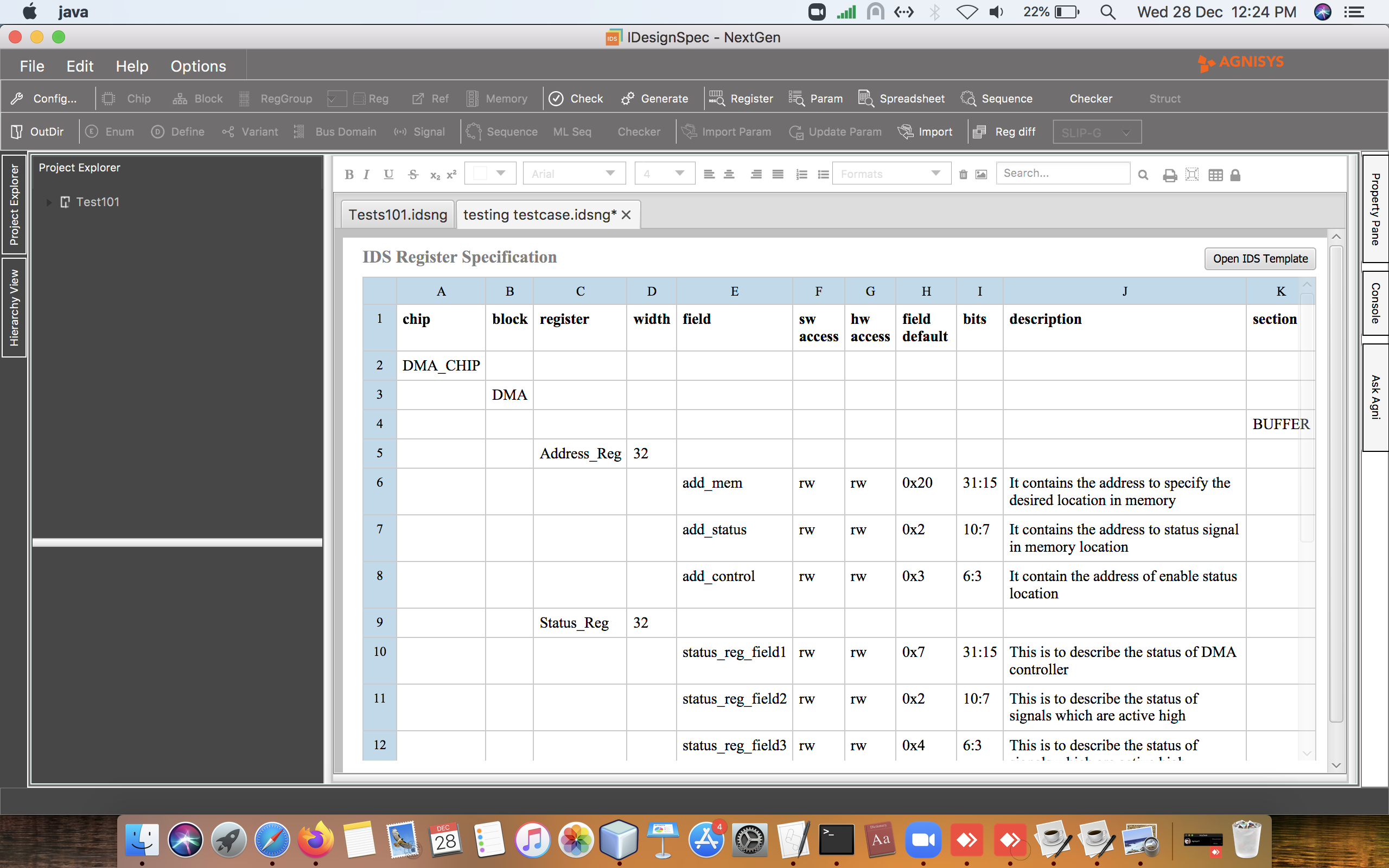

On top of all of this, solutions like IDS-Validate are very straightforward. The entire process is completed using the register information for important standard formats like IP-XACT, SystemRDL, and XML.Users can define the necessary test sequences in a simple editor, then generate the unified test sequences that would enhance the overall efficiency of the process and the end result.

A Purpose-Driven Approach to SoC

As technology continues its rapid evolution, our perspective on SoC itself must evolve with it – particularly when it comes to verification and validation. Make no mistake: these are not two separate concepts anymore and in truth, they haven’t been for quite some time. They’re simply two sides of the very same coin. Creating a single specification format, therefore, becomes a way to guarantee synchronization between the various stages of the process, thus preserving the integrity of the finished product as well.

In the end, it’s about always making sure that you have the right tool for the right job at exactly the right moment. Embracing the ideology at the heart of “shift left” testing, along with tools like IDS-Validate, give you and your teams the best chance to accomplish exactly that.

We invite you to contact us for a free evaluation or to learn more about IDS-Validate.