IDesignSpec Provides Complete Register Design Automation

Published on 05-19-2013 07:30 PM in Semiwiki

It goes without saying that registers play a vital role in designing any ASIC, FPGA, SoC or System. In today’s world, while designing SoC with multiple IPs and functionalities on the same chip, registers stay at the heart of the design right from the architectural level as they are used for key interfaces between hardware, software, firmware and even IPs. Register buses facilitate communication between different IPs and blocks on the chip. Status and configuration registers help in programming the system or SoC in appropriate mode. Although registers can be simple in their own design, their handling needs to be done carefully to attain zero defects. A single bit mismatch can lead to total chip failure.

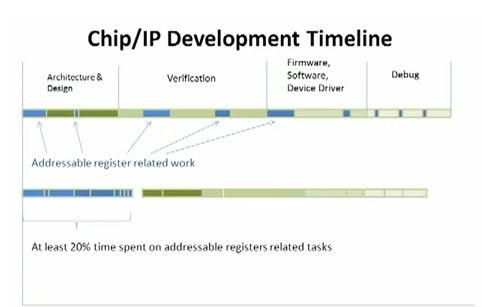

An enormous complexity in handling registers is envisaged in accommodating multiple views of their design (Verilog, VHDL, SystemVerilog, SystemC), requiring different verification methodologies (UVM, VMM, OVM, SystemC and so on) and handling multiple types of bus protocols such as AXI, AHB, APB, Avalon and OCP which may be needed in the overall system or SoC. Designers spend a considerable part (about one fourth) of their design time in register designing, matching, aligning, verifying etc.

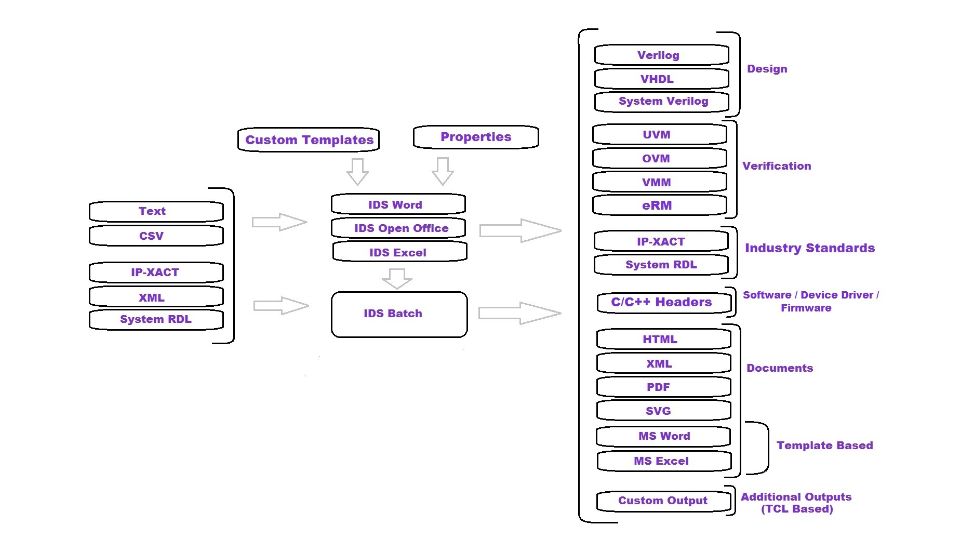

Agnisys has very rightly developed an innovative tool IDesignSpecTM based on their patented technology which automates the overall process of register generation and their sequencing, thereby drastically cutting down the overall design time and improving design team productivity. It reads register specification which can be in as simple as text or standard format like IP-XACT or SystemRDL and generates synthesisable code (Verilog, VHDL or SystemVerilog) as well as verification models (OVM, VMM or UVM).

IDesignSpecTM is a simple light weight application which can be plugged into MS Office. Writing register specification becomes as simple as writing in MS Word or MS Excel. Various configurations can be made for particular registers to be read/write, read only etc. Any conflict in addresses can be checked and corrected. It has self checking templates to prevent errors. All kinds of views of registers can be automatically and quickly generated including C/C++ header files and even documentation which can be in HTML, PDF, MS Word, MS Excel, Framemaker, OpenOffice.org or SVG. User can even specify her/his own customized view of registers to be produced which can be done using TCL or XSLT.

IDesignSpecTM delights the whole cross-functional team including hardware, software, firmware, verification and technical publication personnel as they no longer have to worry about duplicating the effort in developing, verifying, maintaining and documenting registers. Once specified, all views are instantly generated. On any change in the specification, the tool automatically updates all views of the registers at once, eliminating possibility of any error. This makes the handshake between teams smooth, efficient and instant. Re-usability becomes extremely easy, improving the level of productivity further in the long term. Since the process is made automated and error free from the specification stage, it provides uncompromising quality.

IDesignSpecTM handles multi-dimensional registers, memories, configuration tables etc. and is a key enabler to accelerate SoC designs from architecture level to the flow down the line. It has further finer controls (about which I would like to write in future) to enable specific design needs such as coverage specification on registers or blocks, UVM to RTL links at various levels, controlling UVM test sequences etc.