IDS-IntegrateTM The Smart SoC Assembly and Automated

Chip Packaging Solution

- Assemble & package thousands of IP blocks (RTL, IP-XACT, SystemRDL, etc) into a top-level SoC design

- Stitch the IPs together using buses, interfaces, or wires using AI

- Introduce hierarchy, restructure/flatten hierarchy by partitioning

- Access data using Python3, TCL, Java or C++ APIs for improved automation

- Handle all SoC/IP related data (Interconnect, SV, UPF, SDC, CDC, Registers, …) in one place

- Bring-in data(XML, Excel, API) and generate customizable SoC collateral (Documentation, TestBench, Assertions, SystemC models, …)

Automatically Maintain Interconnect Integrity as Specification Changes

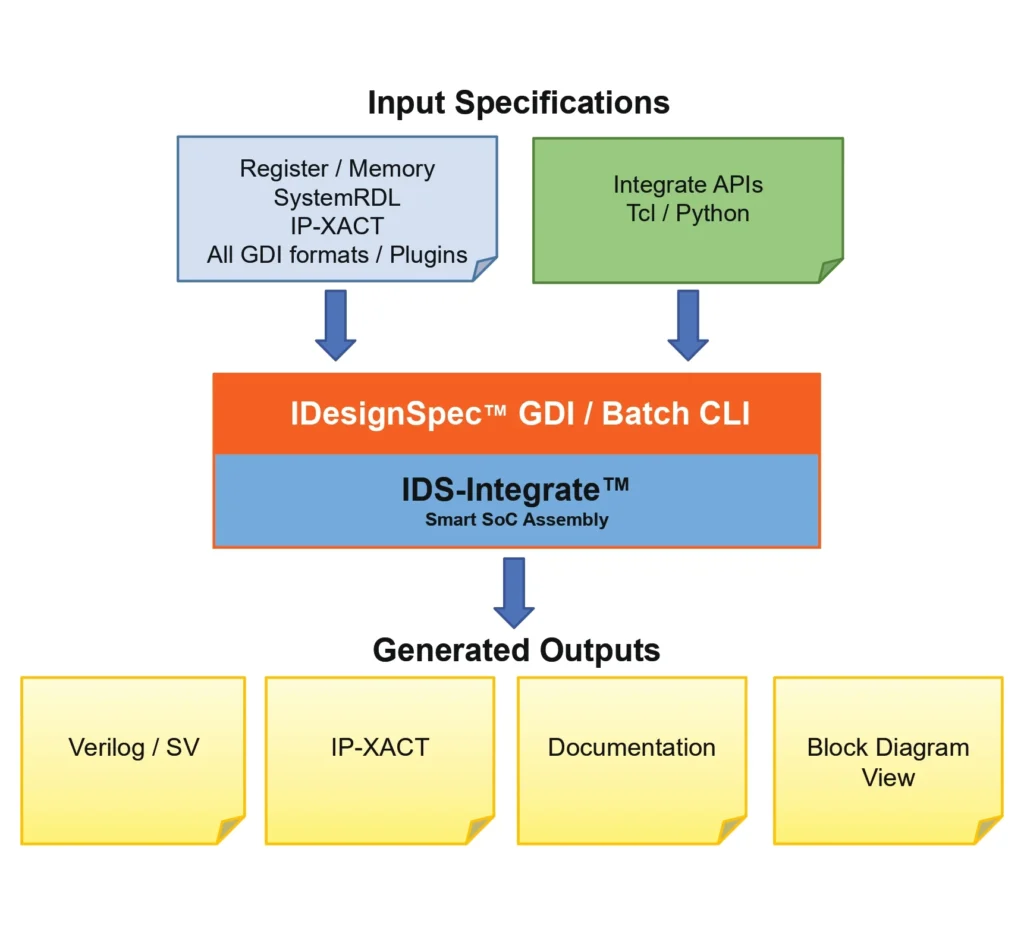

Agnisys solution for SoC Assembly utilizes its specification automation methodology to SoC-level assembly and interconnection. IDS-Integrate provides a flexible and customizable environment to meet the design requirements for your complete chip. It allows users to automatically maintain interconnect integrity as specification changes.

How IDS-Integrate Enhances Your Development Process

IDS-Integrate not only interconnects blocks, but it also generates RTL components such as bus multiplexers, aggregators, bridges (AHB to APB, AXI to APB, and AXI4-Full to AHB-Full), and other “plumbing” components as needed. As expected, IDS-Integrate fully comprehends the register RTL designs generated by IDesignSpec GDI and the IP blocks generated by IDS-IPGen.

You are not limited to designs generated by Agnisys. IDS-Integrate can handle any third-party IP block with an IP-XACT description and can even handle your custom design blocks. You can specify in Tcl or Python how your blocks should be interconnected, including rules for intelligent name-mapping between block input and output ports with identical or similar names. IDS-Integrate assembles the complete top-level SoC based on your specification.

You are not limited to designs generated by Agnisys. IDS-Integrate can handle any third-party IP block with an IP-XACT description and can even handle your custom design blocks. You can specify in Tcl or Python how your blocks should be interconnected, including rules for intelligent name-mapping between block input and output ports with identical or similar names. IDS-Integrate assembles the complete top-level SoC based on your specification.

.

Actions that you can perform with IDS-Integrate include:

- Connecting an IDS-generated block with the your design block and creating a wrapper around it

- Reading an IP-XACT component and connecting with the existing blocks

- Connecting an AHB bus with an APB slave by automatically instantiating a bridge

- Connecting several AHB blocks to an AHB master by automatically instantiating an aggregator

- Moving a block from inside a deep hierarchy several levels higher

- Generating SystemVerilog Assertions (SVA) for connectivity checks using formal verification

Download the IDesignSpec Suite Brochure

View a summary of each product and how the suite enables your semiconductor teams to more rapidly develop products while improving efficiency.