IDS-ValidateTM Automated Pre-Silicon and Post-Silicon Validation

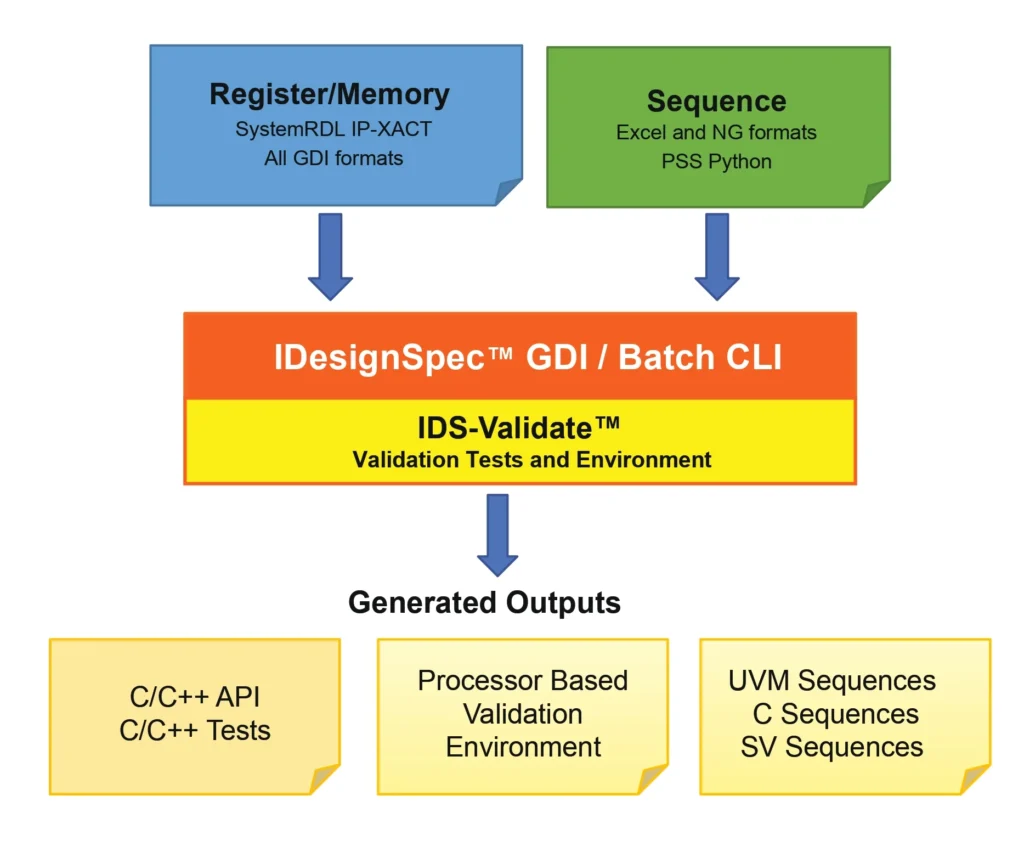

The register verification capabilities of IDS-Verify are extended to your pre-silicon and post-silicon validation by IDS-Validate. IDS-Validate automatically generates both UVM and C/C++ sequences, including specified custom sequences, that exhaustively test your memories and registers. IDS-Validate also extends beyond registers and memories to generate validation environments and user-defined functional tests to verify the functional behavior of your custom design blocks.

Reduction of Verification and Validation Time for SoCs

IDS-Validate is the solution for SOC/IP teams who aim to cut down the verification your validation time. The automatic generation of UVM and sequences enables exhaustive testing of memories and register maps.

IDS-Validate also provides a way to generate custom tests for your boards as well as UVM and UVM-C based environments through Portable Stimulus Standard (PSS) or the GUI-based sequence template in IDS-NG. This provides a solution for your firmware engineers to write and debug their device drivers and application software.

More Details: Getting Started with IDS-Validate

How IDS-Validate Enhances Your Development Process

.

Automatic test generation

From a single specification using IDesignSpec GDI, Python, P5S or Microsoft Excel, you can automatically generate tests that run in UVM and UVM-C/C++ hybrid environments, as well as on physical boards. Thus, IDS-Validate covers both initial pre-silicon validation (also known as hardware-software co-verification) and final post-silicon validation in your bring-up lab.

The generated hybrid environments can run both C/C++ and UVM tests, coordinated by a synchronizer component also generated by IDS-Validate. The environments are capable of handling interrupts and their associated interrupt service routines (ISRs). You can test the connections between your design blocks and use the generated environment as a starting point for developing a complete SoC verification environment.

You can run the generated C/C++ code on your own embedded processors, or you can use a RISC-V SweRV Core EH1 packaged with IDS-Validate.

Automation of portable sequences from a specification

IDS-Validate also unifies the creation of portable sequences from a golden specification. You can capture sequences in Python, P5S spreadsheet format, or the Sequence view of IDesignSpec GDI and generate multiple output formats for a variety of domains:

- UVM sequences for verification

- SystemVerilog sequences for validation

- C code for firmware and device driver development

- Specialized formats for automated test equipment (ATE)

- Hooks to the latest Portable Stimulus Standard (PSS)

- Documentation outputs such as HTML and flowchart

- Programmers Reference Manual (PRM) which gives Register and Sequence along with a flowchart view

The sequence constructs include loops, if-else, wait, and switch statements to change the interfaces, specify encoding formats, deal with time-unit differences, use macros, specify variants, and use return statements to return user errors from sequences. The constructs support constrained variables for randomized sequences, and handling of indirect and interrupt registers.