Enhancing RTL Design: Alias Register Support with Lock Mechanism in RTL Design

Alias Registers in RTL Design:

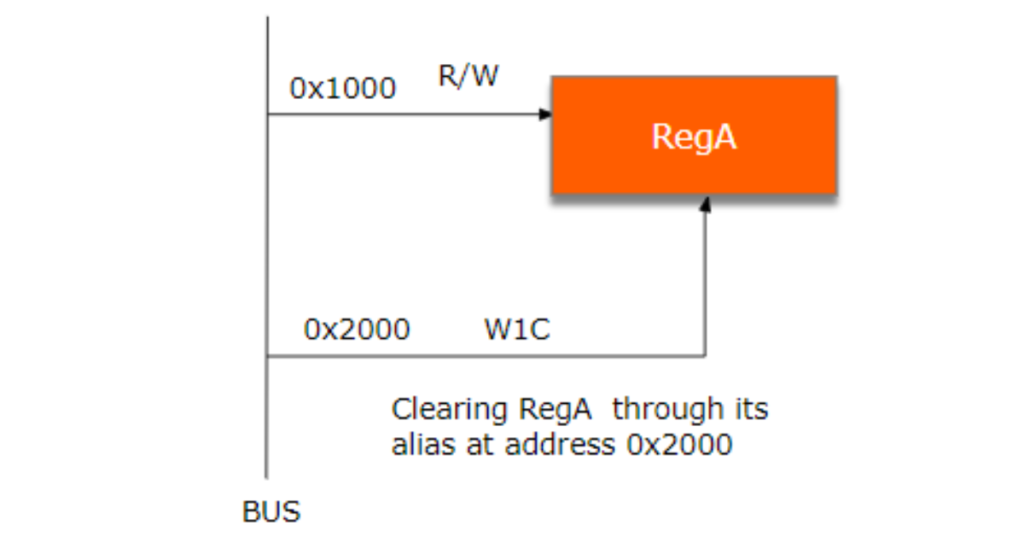

An alias register is a hardware feature that allows multiple names or addresses that refer to the same physical register, making registers accessible from multiple addresses in the same address map. The fields in aliased registers may have different behavior based on the addresses used to access them. This implies the fields in a register may be readable and writable when accessed using one address, but read-only when accessed from another.

Alias registers can map to the same memory location or share hardware resources, making them particularly useful in scenarios such as:

Memory-Mapped Registers: Where multiple addresses or names refer to the same register, facilitating easier interaction with peripheral devices

Multi-Context Hardware: Allowing different hardware contexts to access shared resources without redundancy

Alias registers are often employed in system on chip (SoC) designs, where different subsystems may need to interact with shared resources. By allowing multiple aliases, designers can create flexible and modular architectures.

In the Agnisys IDesignSpec™ (IDS) Suite, users can create aliases of a register or a field by applying the “alias” or “ids_alias” property. By using IDS, if a register has multiple fields then some of its fields can be aliases of other register fields and some can be just normal register fields. IDS also supports alias registers that are indicated with repeat in both Verilog and SystemVerilog/Universal Verification Methodology (UVM) output.

Importance of Lock Mechanisms in RTL Design:

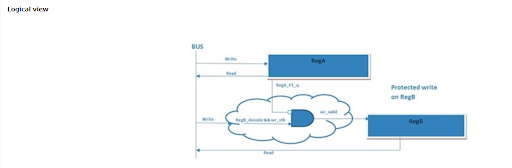

The software write access of a register can be locked based on the value of another register field or based on an expression consisting of different register fields or some external signal declared as input. Such a register for which the write access is locked is a “lock register,”

Concurrency in RTL design can lead to data hazards, race conditions, and other issues that compromise system reliability. Locks can be used to ensure exclusive access to a register or to manage read/write operations in a coordinated manner.

In IDesignSpec, a lock register is created by specifying the property “lock” on the register. The value of this property is the hierarchical path to another register field, depending on which the software access of the register is locked. The value of the lock property can also be an expression consisting of different register fields and, if the expression is true, then the register becomes read-only but is otherwise a read-writable register.

Types of Lock Mechanisms in IDS:

Read Locks: Allowing multiple read operations simultaneously while blocking writes. In IDS this operation can be achieved by using the property lock_r.

Read-Write Locks: A more flexible mechanism allowing multiple readers or a single writer. In IDS this operation can be achieved by applying the property lock either on a reg or field.

Verilog Implementation of Alias Registers with Lock Mechanism::

Lock mechanisms are critical for ensuring that access to alias registers is controlled, preventing concurrent write operations or invalid read operations. While alias registers offer several benefits, they can introduce issues such as data inconsistency and race conditions, especially in concurrent environments. Implementing a lock mechanism helps to mitigate these issues. In IDesignSpec alias and lock can be used together supported for register and field components both.

Case Study: Applying IDS in a Complex SoC Design

To illustrate the effectiveness of IDS, let’s consider a case study where IDS was used to generate RTL for a complex SoC design. For multimedia processing, the design used individual registers for each data stream’s configuration and control, leading to a large number of registers and increased complexity. Additionally, concurrent access to these registers by different processing units sometimes resulted in race conditions, causing data corruption and system instability.

To address these issues, the designers decided to use IDesignSpec to implement alias registers with a lock mechanism. Common configuration settings and control data could be shared across multiple data streams. In addition, alias registers were created to reference the same physical register, which reduces the number of registers. A lock register was introduced to control access to each set of alias registers, which ensured that when one processing unit was updating the register, other units were prevented from accessing it until the update was complete. This results in significant security improvements.

How IDS uses alias and lock properties together in SystemRDL:

This specification has been created using the specialized RDL editor for VS Code. More details can be found here :

https://marketplace.visualstudio.com/items?itemName=AgnisysInc.agnisysrdl-beta

property ids_alias { type=string; component=reg|field;};

property lock_r { type=string; component=reg|field;};

addrmap block_1 {

reg r1 {

field {

sw = rw;

hw = na;

lock_r = "!r2.f";

ids_alias = "r3.f";

} f1[0:0]= 0x1;

};

reg r2 {

field {

sw = rw;

hw = r;

} f[0:0]= 0x1;

field {

sw = rw;

hw = r;

} f22[2:2]= 0x1;

};

reg r3 {

field {

sw = rw;

hw = r;

} f[0:0]= 0x1;

};

r1 r1;

r2 r2;

r3 r3;

};

RTL Output:

assign r1_wr_valid = r1_decode && wr_stb ;

assign r1_offset = block_offset +'h0;

assign r1_decode = (address[addr_width-1 : 0] == r1_offset[addr_width-1 : 0]) ? 1'b1 : 1'b0;

assign r1_rd_valid = r1_decode && rd_stb ;

assign r1_f1_q_temp = !(!((r2_f_q))) ? r1_f1_q : 1'b0;

assign r1_rd_data = r1_rd_valid ? {31'h0, r1_f1_q_temp11} : 32'd0;

Conclusion:

Alias registers with lock support are a powerful concept in RTL design, offering flexibility and safety in hardware systems. By integrating lock mechanisms, design engineers can ensure data integrity and avoid concurrency-related issues. Proper implementation of these mechanisms is crucial for building robust and reliable hardware architectures, especially in complex systems like SoCs.

By understanding the intricacies of alias registers and lock mechanisms and by using IDS, RTL design engineers can create efficient, safe, and scalable hardware designs.