Hardware/Software co-design and co-verification of embedded systems with Registers

Introduction

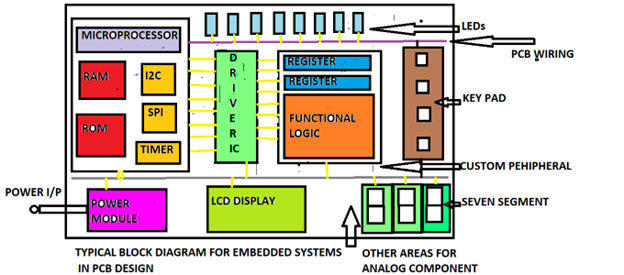

Usually, Any Digital Peripheral Custom IP is divided into two sections. One is designed logic circuits based on their specifications or functionality and the second Registers which are used for configuring, sending, and receiving data to and from Initiator and sending and receiving data from external devices. These Registers act also as input for internal functional circuits that send data to the output pin of IP and the programmer with this status of the pin/port drives external devices in the Embedded world. So Hardware/Software Co-design and co-verification are needed before complex IPs tape out in the market. Day by day this is becoming harder and tedious. This problem should be solved in time otherwise the Complex peripheral’s NRE(Non-Recurring Engineering) cost would increase and the Embedded system failure rate will be high and may be dangerous to Application industries like Automotive, Avionics, Medical and Communication etc.

Approach:

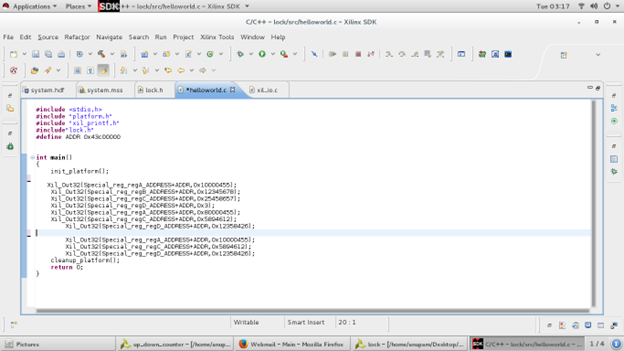

With our approach, the programmer can write data on IP’s Registers from the Software side These Registers’ values must be equal to their expected values according to functionality at any time after reset or default conditions. These register values ensure IPs are working functionally well. In Embedded Systems, those Registers are used in application programs. So data must be written on or read the correct value from the correct address locations of registers. We solve this problem through the Hardware-Software interface by making Prototypes and their Verification, and Validation. We use HDL languages for RTL generation, UVM for Verification, and Embedded C for Validation, independent from any Processor, for Simple registers and Complex Registers and checked their functionality like lock, shadow, aliasing, TMR, Trigger buffer, RW pair, FIFO, Counters, etc. These Simple and Complex Peripheral Registers have been validated and can be used in UART, I2S, GPIO, EEPROM, Dual Port RAM, or any custom IPs for Embedded Applications.

For the Co-design and Co-verification approach, we need four crucial parts of this technique:

1-Register Specification in RDL format

2-RTL generation

3-Register map ( header files)

4-UVM Code for Verification Environment

5-C-API and C-Code for Validation Environment

All the above will go through a process to ensure IP will work functionally well in the Embedded domain.

Example:

LOCK Register

APPLICATION-1

If these Registers which are used in Custom Peripherals are already validated, we need to just connect with functional logic, and registers are interconnected according to the Application. So due to Co Design and Co Verification /Validation simultaneously Time to Market reaches to minimum value and these Registers are reusable for different Custom IPs without Verify again, only testing the requirement of functional block inside IP. Registers are Validated at every test sequence and all aspects are taken into consideration with corner cases.

APPLICATION-2

In the above Application, a sample Receiver block diagram is shown, which takes data as start-address-command-data in one packet. Stop condition will stop and the beginning of the next packet. A sequence Detector detects and starts to enable data through mux, counter control will ensure parts of the packet will be stored in 8-bit each, in particular Register. 8-bit length will be as input to another counter and for this length, data will be stored in the data register. e.g if the length is all 8-bit is one, 256-bit data will be stored. The processor will set the baud rate and Configure registers.

In this example registers and counters are major parts of the block diagram. If those are Verified and Validated already and reused here, no further verification of these parts is required.

Results:

Our approach is so many percent faster (reducing cycle time by as much as 30%), cheaper, smaller, or better than something else. This approach can generate results simultaneously with testing in the Verification and Validation environment for Hardware and Software together..

Conclusion:

Our solution is a generalized approach for any Custom Peripheral IP. Our approach directly works on the Embedded real world and It has changed the world. Contact us