Improving Design Productivity and Quality with Specification Automation

Designing semiconductor devices has always been a distinct specialty of engineering, but today’s designers face immeasurably greater challenges. A typical system-on-chip (SoC) design has billions of transistors, thousands of intellectual property (IP) blocks, hundreds of I/O channels, and dozens of embedded processors. Chip designers need all the help they can get.

Three Keys for Faster, Better Design

Assistance comes in three forms: abstraction, automation, and reuse. Virtually all chip design today occurs at the register transfer level (RTL), enabling much greater productivity than manually crafting gates or transistors. This level of abstraction is therefore much more efficient, making it possible for a single designer to create entire IP blocks or even subsystems.

RTL design is also amenable to automation; generating gate-level netlists automatically via logic synthesis is part of what makes the design process so efficient and productive. Just about every aspect of the test insertion, power management, layout, and signoff flow that follows RTL design is automated as well. Without this approach, modern SoCs simply would not be possible.

The third form of assistance is design reuse. Especially for standard IP blocks and interfaces, there is no value-add in reinventing the wheel by designing from scratch. EDA vendors and dedicated IP providers offer a huge range of reusable designs, most in RTL form. Designers often need this IP to be configurable and customizable, so it may come from a generator rather than as a fixed design.

Register Automation Is the Foundation

All three forms of designer assistance come together in specification automation, starting with the registers in the design. SoCs typically have a huge number of addressable (memory-mapped) registers defined by the chip specifications. These registers form the hardware-software interface (HSI) by which the embedded software and system drivers control the operation of the hardware.

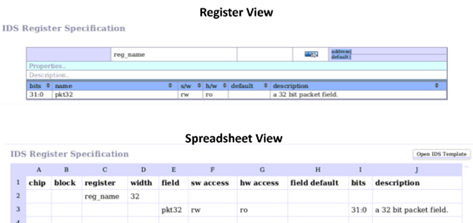

Manually writing RTL code for all these registers is tedious and error-prone. Fortunately, the Agnisys IDesignSpec™ Suite makes it easy to automatically generate the register RTL design. Using the IDesignSpec GDI interactive tool or the IDS-Batch™ CLI Batch Tool, designers create their RTL files at the push of a button every time the register specification changes.

These tools accept many register and memory specification formats, including spreadsheets, SystemRDL, IP-XCAT, and the Portable Stimulus Standard (PSS). Designers can specify many widely used special register types, including indirect, indexed, read-only/write-only, alias, lock, shadow, FIFO, buffer, interrupt, counter, paged, virtual, external, and read/write pairs.

Generating Other RTL Code

Registers are just one part of a chip that can be specified abstractly and generated automatically, fostering reuse and improving quality of results (QoR) with proven design IP. Another example is interfaces to standard buses such as APB, AHB, AHB-Lite, AXI4, AXI4-Lite, TileLink, Avalon, and Wishbone. The RTL design generated by IDesignSpec Suite includes any interfaces requested.

Any necessary clock-domain-crossing (CDC) logic across asynchronous clock boundaries is also included in the generated design. For safety-critical chip applications, designers can request that safety mechanisms such as parity, error-correcting code (ECC), cyclic redundancy check (CRC), and triple module redundancy (TMR) logic be included as well.

Most chips contain standard design elements such as AES, DMA, GPIO, I2C, I2S, PIC, PWM, SPI, Timer, and UART. Designers specify these blocks with many degrees of configuration and customization, and the Agnisys IDS-IPGen™ design tool generates the RTL design code. IDS-IPGen also generates finite state machines (FSMs) and other design elements for custom IP blocks.

Automating SoC Assembly

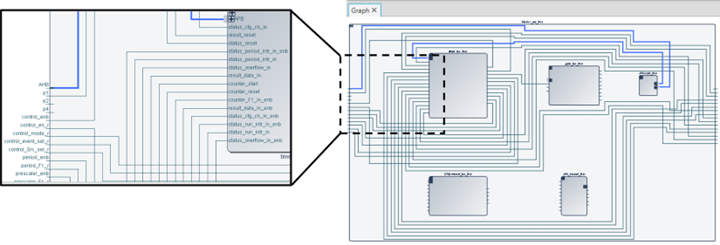

As noted earlier, SoCs contain thousands of standard and custom IP blocks. All of these must be connected together into the top-level chip design. Like register design, manually writing the RTL code for this stage is a tedious and error-prone process. Block inputs and outputs change many times over the course of a project, and updating the top-level RTL code by hand is extremely inefficient.

The Agnisys IDS-Integrate™ design tool, another part of the IDesignSpec Suite, automates the chip assembly process. Designers specify the desired hookup using a simple but powerful format that includes wildcards to handle buses and collections of signals with similar names. IDS-Integrate automatically generates the complete top-level RTL design.

For IP blocks with standard buses, IDS-Integrate automatically generates any required aggregators, bridges, and multiplexors, including them in the top-level RTL design. For example:

- AHB interfaces on two IP blocks can be aggregated into a single bus

- An AHB-to-APB bridge can connect IP using AHB and IP using APB

Summary

With the burden on SoC designers growing all the time, they need to specify at the highest possible level of abstraction, take advantage of automation, and reuse whenever possible. The specification automation capabilities of the Agnisys IDesignSpec Suite provide all three forms of designer assistance, providing the industry’s most complete solution.

Designers no longer have to hand-write RTL code for registers, memories, standard bus interfaces, aggregators, and bridges, CDC logic, safety mechanisms, custom IP elements, standard IP blocks, and top-level design. Abstract specification and automation improves productivity; reuse of proven IP improves quality of results.

Customization and configuration options ensure that designers do not have to sacrifice any flexibility to achieve these benefits. Many other project teams—verification, validation, embedded software, bringup, and documentation—also benefit from specification automation. The reasons to select Agnisys as a design partner are truly compelling.