SEMICONDUCTOR DESIGN AND VERIFICATION ARTICLES

Our Latest Blogs

Agnisys Inc. was established in 2007 in Massachusetts, USA, with a mission to deliver innovative automation to the semiconductor industry...

Modern SoCs get more and more complicated every day. As the complexity of modern electronic semiconductor device design increases, niche...

Introduction As per the IP-XACT User Guide, IP-XACT defines an API called Tight Generator Interface (TGI) to query, modify, create...

By Louie De Luna, Agnisys Chief Product Evangelist...

Just about a year ago, I published a blog post about the emerging need for better functional safety and security...

By Louie de Luna, Agnisys Director of Sales and Marketing...

Moore’s law prediction about the increase in density of an SoC design continues to prove accurate with each advancement of...

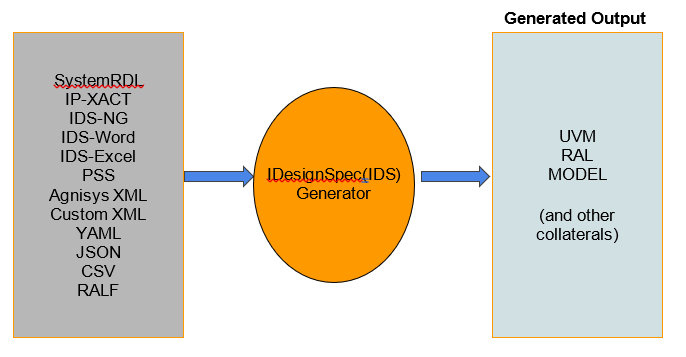

Typically thousands of registers are required for today’s complex designs, which are used to control the operations of the SOC...

It’s hard to think of any electronic design automation (EDA) innovation that’s had more impact than the Universal Verification Methodology...