SEMICONDUCTOR DESIGN AND VERIFICATION ARTICLES

Our Latest Blogs

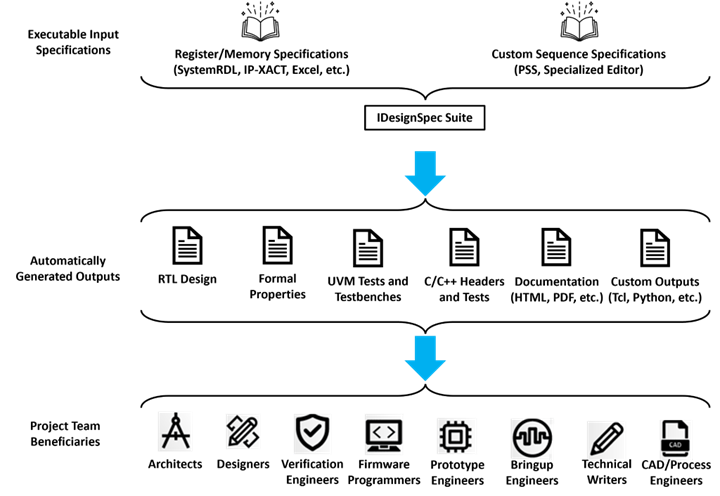

IDesignSpec™ empowers users with approximately 450 properties that enable extensive modification of the structure and behavior of generated outputs...

The Agnisys IDesignSpec™ (IDS) suite offers powerful support for reading third-party data in various formats, including industry-standard formats like...

The Agnisys IDesignSpec™ Suite is certified for functional safety standards like ISO 26262 and IEC 61508, supporting all ASIL...

Maintaining a single golden specification is essential for consistency in chip development. Traditional workflows often lead to synchronization challenges...

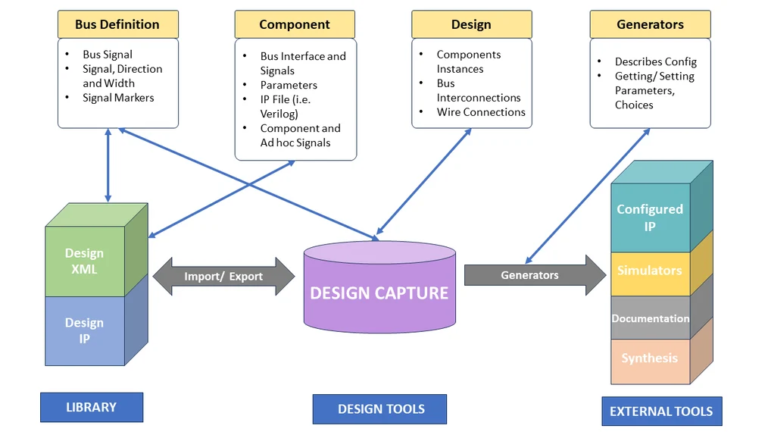

Agnisys was founded on a deceptively simple idea: automatic generation of as many IP and system-on-chip (SoC) development files...

There is probably no hotter topic in electronics right now than artificial intelligence (AI). AI was a fringe technology for...

SystemRDL (System Register Description Language) plays an important role in the life cycle of System-on-Chip (SoC) development, facilitating efficient design...

Designing semiconductor devices has always been a distinct specialty of engineering, but today’s designers face immeasurably greater challenges. A typical...

Introduction Assertion-based verification (ABV) is a powerful methodology used in modern hardware design verification. By embedding assertions within the design...