SEMICONDUCTOR DESIGN AND VERIFICATION ARTICLES

Our Latest Blogs

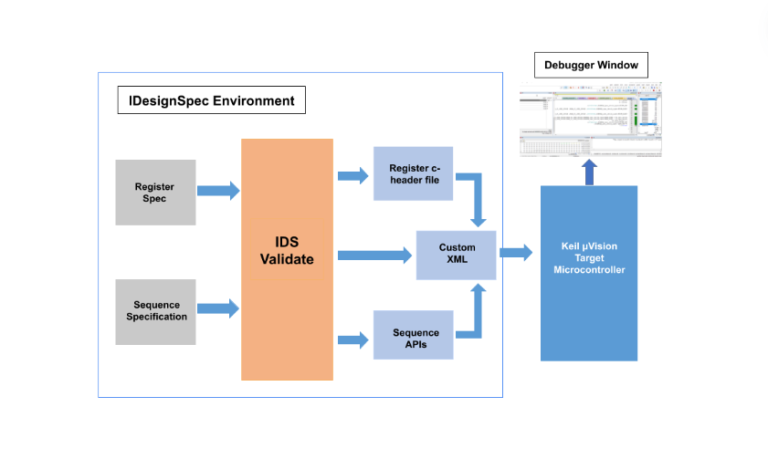

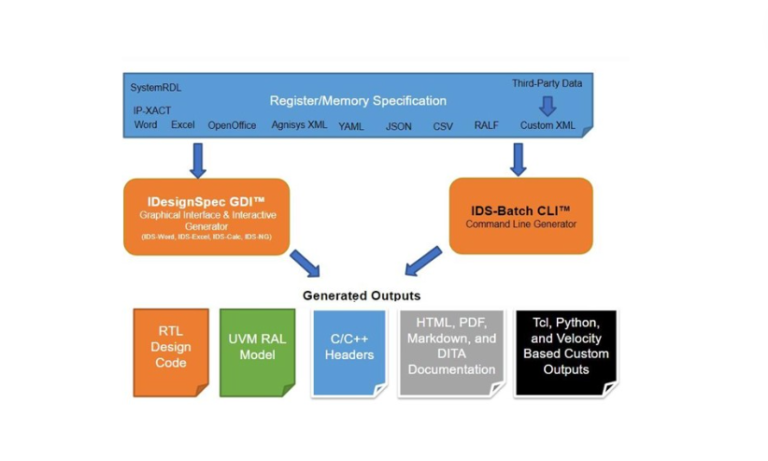

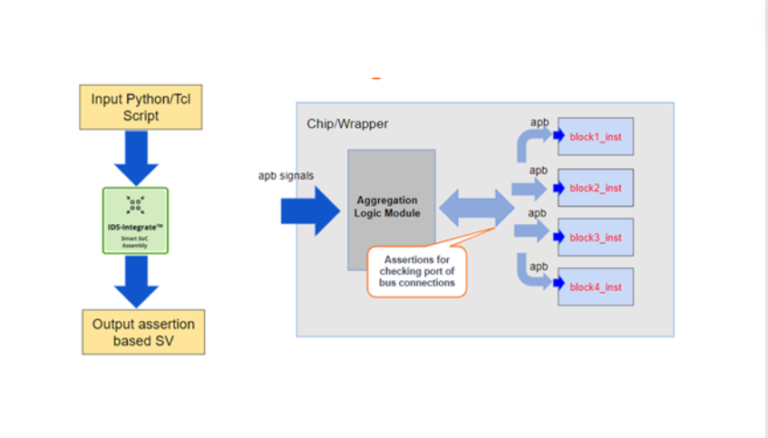

IDesignSpecTM (IDS) is a product suite that improves the productivity of FPGA/ASIC, IP/SoC, and System Development teams. These products encompass...

Introduction IP-XACT stands for Intellectual Property exchange-Advanced Configuration and Integration of IP components. It is an IEEE standard (IEEE 1685)...

Register automation is an integral part of IP and SoC development. Long ago, design, verification, firmware, and documentation teams preferred...

Introduction In the field of hardware verification, the Universal Verification Methodology (UVM) is a powerful framework that provides a systematic...

SystemRDL, or System Register Description Language, is a specialized hardware description language (HDL) used for specifying registers in digital systems...

Introduction The IDesignSpec™ Suite by Agnisys stands as a versatile solution, simplifying the capture of hardware/software specifications in diverse formats...

In the dynamic landscape of Very Large Scale Integration (VLSI) design, the ever-growing complexity of Application-Specific Integrated Circuits (ASICs) has...

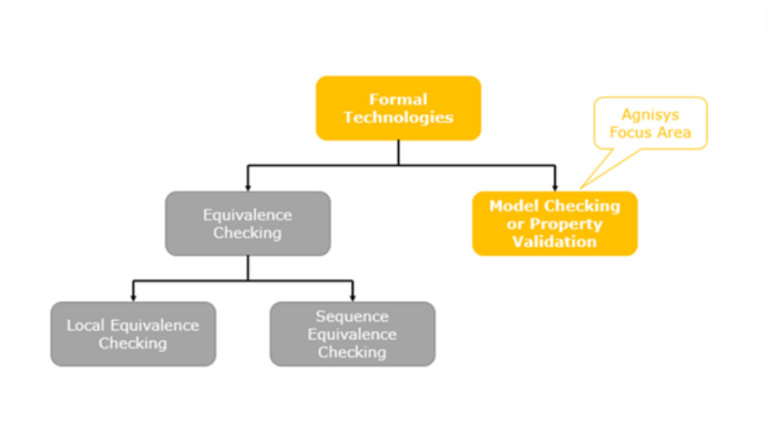

Formal verification is a crucial aspect of ensuring the reliability and safety of systems. ARV stands for Automatic Register Verification...