SEMICONDUCTOR DESIGN AND VERIFICATION ARTICLES

Our Latest Blogs

Agnisys is an Electronics Design Automation (EDA) company offering tools to automate specification to IP and SoC design and development...

Developing semiconductor intellectual property (IP), system-on-chip (SoC) designs, and complete systems is enormously challenging. Even a small error in the...

As chips get ever larger and more complex, one thing is for certain: the electronic design automation (EDA) tools, techniques...

Modern system-on-chip (SoC) devices get more and more complicated each and every day. As the size and complexity of modern electronic...

Late last year, I published a blog post that summarized what had transpired for Agnisys over the course of 2021...

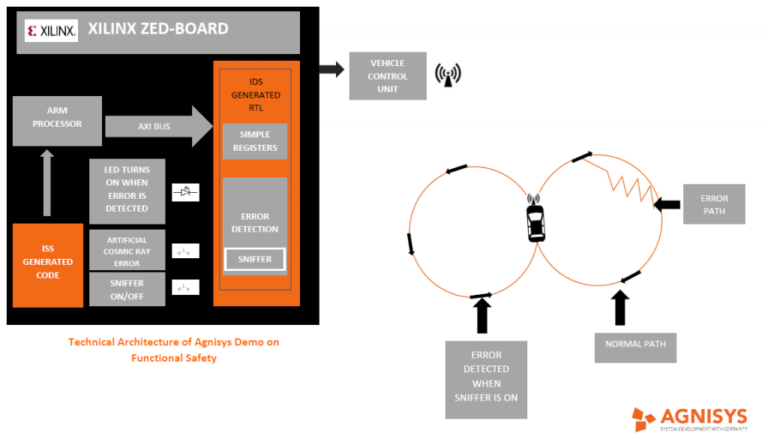

The Intersection of Functional Safety and Electronic Design In an industry that has gone through an incredibly rapid transformation over...

Register-transfer-level (RTL) code, formal analysis, RTL simulation, and logic synthesis have all raised the abstraction level of electronic design and...

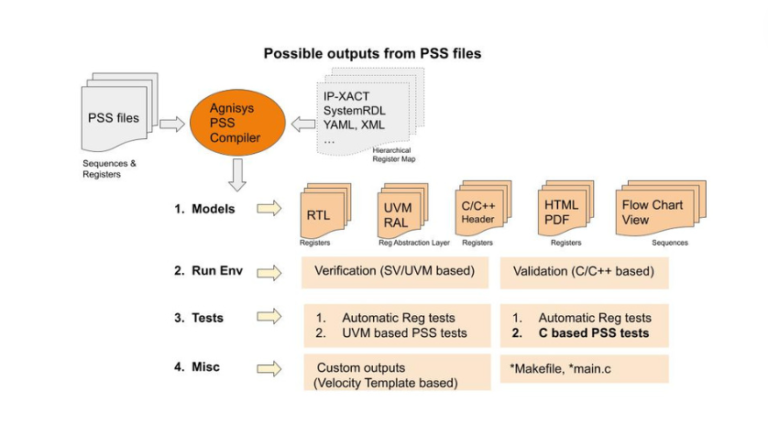

The Agnisys IDesignSpec™ Suite offers development teams a closely linked set of products, including a unified graphical design interface (GDI)...

The UVM register model is an essential component of the UVM-based verification for modern designs. In this article, we discuss...