Questa® VIP validates IDesignSpec generated IP

In our domain, we automatically generate registers and memory interface which can interface with all the standard bus protocols. If we take a look at the AMBA®AXI4Lite bus protocol, it has different channels for reading, writing. All these channels are designed to work simultaneously and this gives rise to a lot of complexity in the verification of the protocol. So verification with constrained resources to deliver reliable results within very tight schedule is challenging, to say the least.

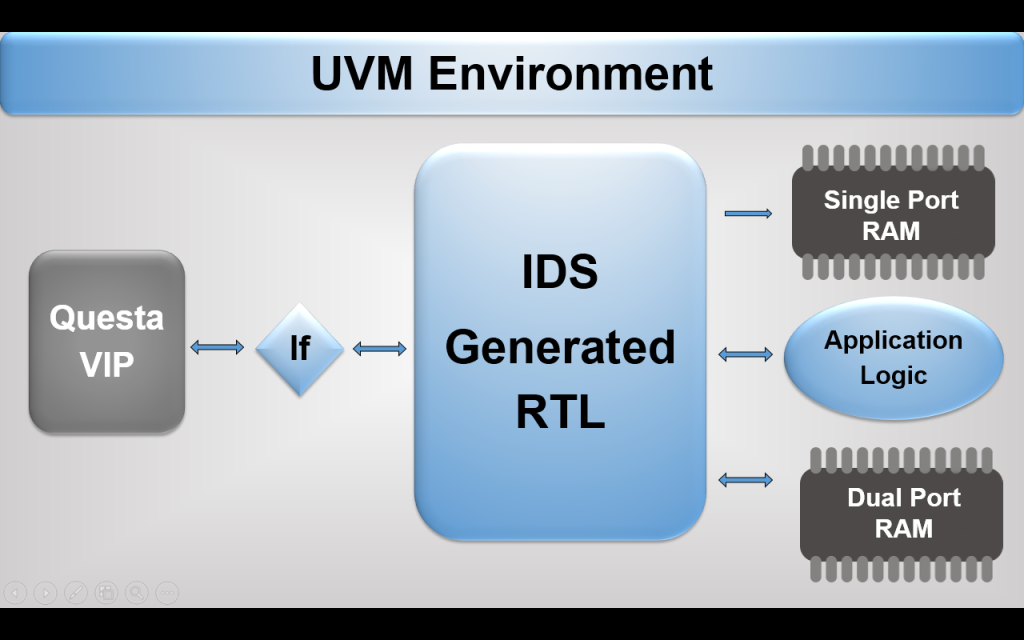

One of the outputs from our IDesignSpec product is the Bus client RTL. The generation of this IP is challenging since what gets generated is based on the specification that the user provides. Testing out such dynamic designs is a huge task since the customer can create any possible specification. So it is not a static IP that needs to be verified, nor is it a configurable IP. It really is a generated IP, so the task is an order of magnitude more complicated.

We were fortunate enough to get access to Questa® VIP (QVIP) for our design IP verification. One of the most time-consuming aspects of verification is creating a testbench that covers all testcases. So AMBA AXI4Lite contains so many testcases, Questa VIP provides a huge benefit to verify the DUT by plugging it into the testbench.

QVIP enabled our team to verify the bus interfaces quickly and thus reducing the effort required by the engineers to develop a very comprehensive verification solution. As a result we were able to focus on other crucial task in our project and also maintaining the quality and reliability of our design as expected by our customers.

Questa VIP validates IDesignSpec generated IP

QVIP is easier to use and provides plug-n-play verification environment to verify the IP design and it has enabled the achievement of higher functional coverage results. It provides comprehensive test suite, which is well documented and covers all scenarios. The test suite contains example for simple read write, for coverage, example to check backdoor access and for ARM® compliance that contains the ARM assertions to verify the IP design. It covers memory models with delays and provides proper response signals for the read and write transaction.

It covers simple read write transaction, back to back read write transaction with n cycle delays, simultaneous read and write transaction from different address channels, read and write channel with n cycle delays and so on. It helps to verify dual port and single port memory which is connected to the slave side. And it also verifies the custom logic at the slave side. QVIP allows the closed loop verification, where it provides the verification plan and has inbuilt scoreboards to collect the coverage data.

The QVIP enabled us to easily find bugs that would have been hard to reach if we had not used the VIP. We rely on Mentor Graphics for its complete verification IP solutions and excellent customer support. They enabled us to give proof positive to our customers that our generated IP is compliant with the protocols.