Specification Automation for Designers

Improved technology for remote learning emerged as one positive outcome amid the challenges of the last year and a half. Online talks, webinars, and podcasts are nothing new, but with so many people working at home the importance of virtual options has grown. When did a vendor last visit your company in person to discuss a new tool or technology? When was the last time you attended an in-person conference or seminar? For many engineers, it has been well over a year since we were even in the office. We’ve relied on the web for just about everything.

At Agnisys, we’ve been doing regular webinars since well before the pandemic and they have been highly effective and successful. We offered a series last year that proved quite popular, and you may have noticed that we recently announced a new series that began a few weeks ago. With interest in remote learning at an all-time high, we fully expect a great turnout for all our upcoming virtual events. Even if you’ve attended some of our webinars before, I encourage you to check out our new series because we’re taking a dramatically different approach to the material.

This time, we’re focusing on the requirements for different project teams and different tasks in the system-on-chip (SoC) development process: hardware design, simulation, formal verification, firmware coding, system-level validation, and more. The focus is not so much on individual products but rather on how they work together to automate multiple stages of the process from executable specifications. We do talk a lot about our relatively recent IDS NextGen (IDS-NG™) solution, which provides a common front end and “dashboard” for all our users on the various teams.

As one example, consider the “IDS-NG for Design” webinar that we presented on June 10. We highlighted current challenges for chip designers and demonstrated how our specification automation solution offers multiple ways to assist. These challenges include:

- Designing huge, complex sets of control and status registers

- Properly handling clock domain crossings

- Obtaining robust but flexible IP for standards-based blocks

- Supporting complex bus protocols

- Interconnecting IPs and custom blocks

- Satisfying functional safety and security requirements

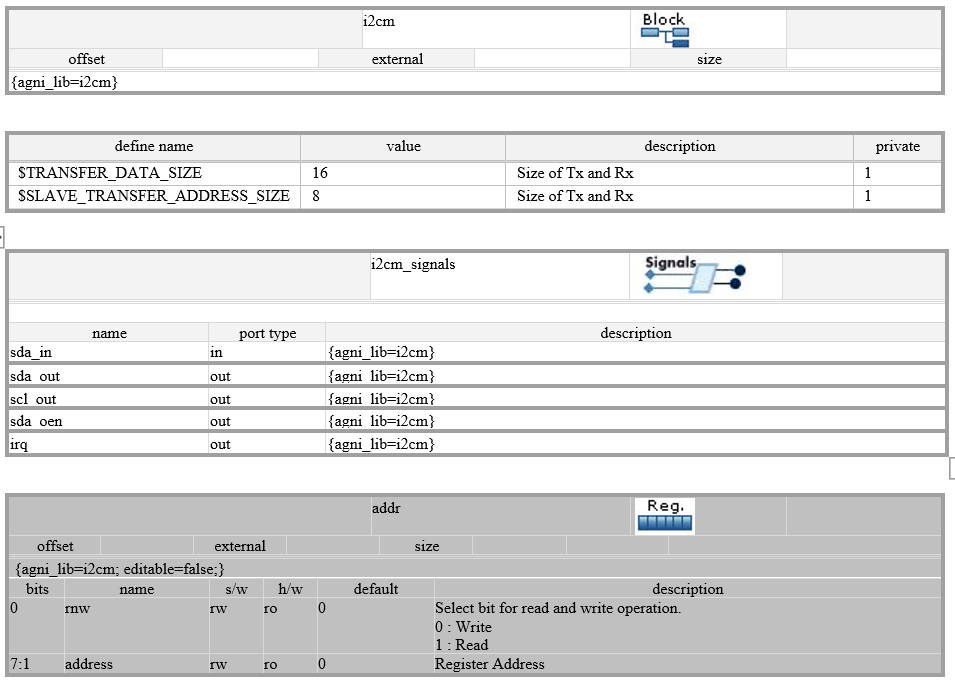

We significantly reduce the amount of register-transfer-level (RTL) code that the designers need to write by generating several parts of the design from executable specifications. Register automation is probably the best-known example, and we have been the industry leader in this area for many years. You can specify your registers, register fields, register files, register groups, and memories in an intuitive specification editor within IDG-NG. You can also import existing specifications in a wide range of popular formats, including the SystemRDL standard, and modify them in the editor if you wish.

We generate the complete RTL design for the specified registers, relieving the design team of any related coding work. We make the designers popular with other teams on the project, since we also generate Universal Verification Methodology (UVM) models for the verification engineers, C/C++ headers for the embedded programmers, and documentation for the technical writers. This eliminates bugs related to different interpretations of the specification or to using different versions of the specification. Every spec change results in re-generation for all teams, so they remain in sync.

We also generate the RTL code necessary to avoid metastability and other problems on clock domain crossings (CDCs). When we create the registers, we detect when they are in a different clock domain than the system bus, or when they are in a unique clock domain distinct from the system bus and the rest of the hardware design. We support several well-proven types of synchronization across the CDC boundary, including two-level flip-flop, multiplexor, and handshake. We also help the verification team by generating the relevant assertions for CDC formal analysis.

Just last month, I discussed the challenges of standards-based IP and presented our SLIP-G™ library of IP generators. Designers have many options to configure and customize the IP blocks that we generate. Our currently supported standards include General Purpose Input/Output (GPIO), I2C, Timer, Programmable Interrupt Controller (PIC), Direct Memory Access (DMA), Serial Peripheral Interface (SPI), Pulse Width Modulation (PWM), and Advanced Encryption Standard (AES). In all cases, we generate the RTL design, UVM models, programming sequences, and documentation.

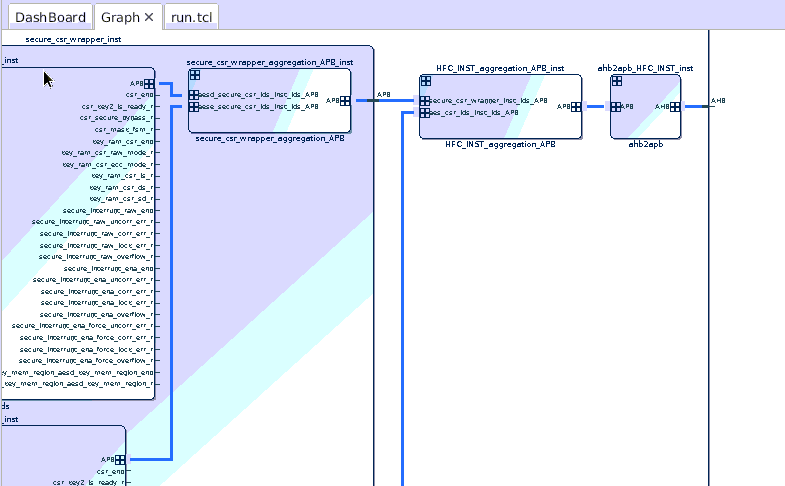

A typical SoC has many thousands of blocks, some standards-based IP, some licensed from other sources, and some custom-designed. Assembling all these blocks into the top-level chip is a large and rather tedious task. Fortunately, IDS-NG automates this process for you as well. As you would expect, we generate all the RTL code needed to interconnect blocks from SLIP-G. We also give you the ability to specify how custom blocks should be integrated, and we generate that part of the RTL design as well. Finally, we generate RTL aggregators, bridges, and multiplexors for standard buses as needed.

The webinar goes into much more detail about how these capabilities benefit the design team, and you can view a recording here. At this same location, you can view the complete list of webinars in the series, view any that have already occurred, and register to attend upcoming webinars live. Even after many of us return to the office, we believe that online learning will continue to be of high value and high interest. We’re deeply grateful to those of you who have been supporting our efforts, and we invite everyone else to register and join the fun. We’ll see you online!