Specification Automation for Embedded Programmers

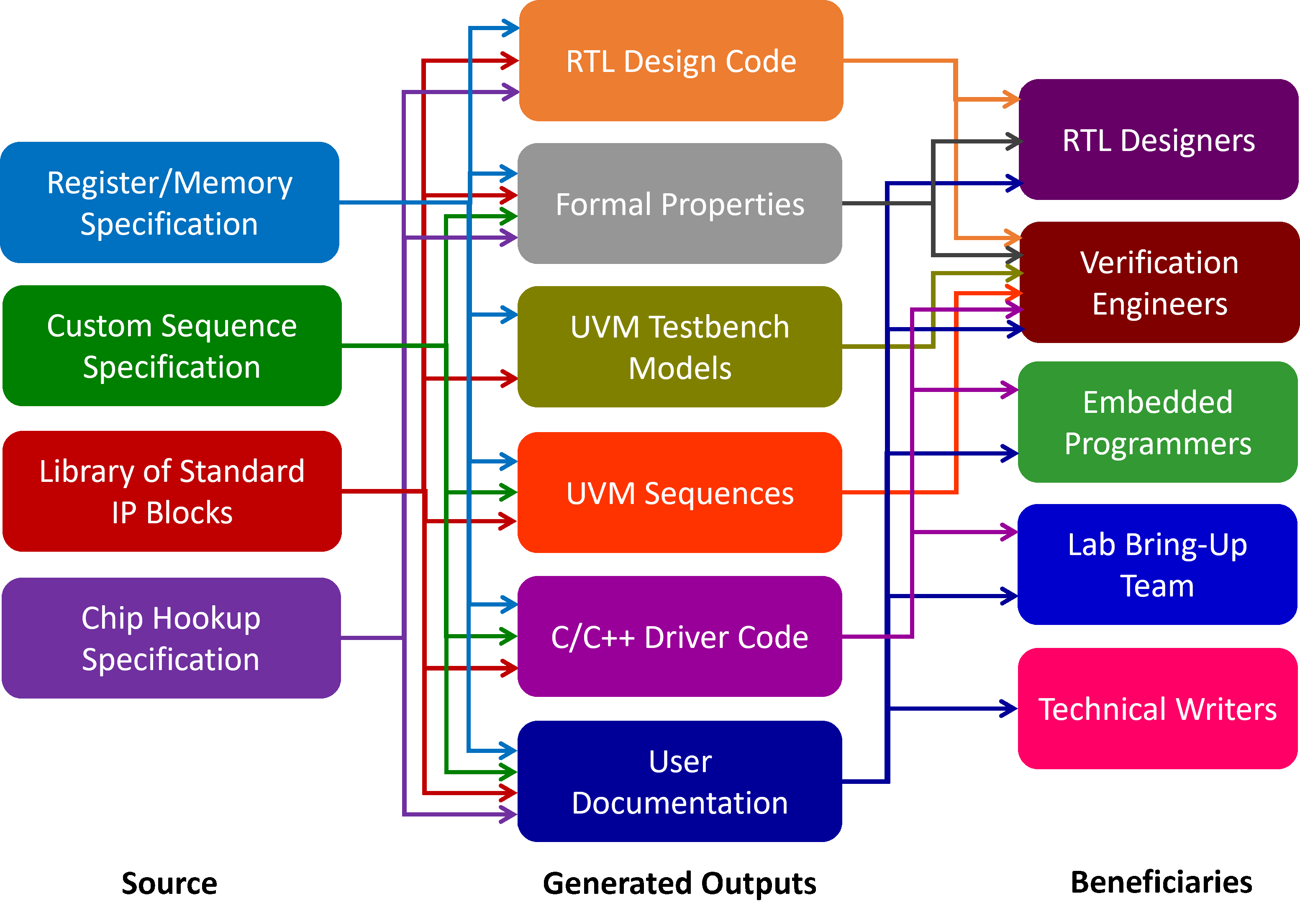

As an electronic design automation (EDA) company, Agnisys provides many benefits for chip design and verification engineers. Our specification automation solution generates both the register transfer level (RTL) design and key elements for verification with simulation and formal tools. As the diagram below shows, our solution also provides value to other teams. In this post, I’d like to focus specifically on embedded programmers, since we are seeing increasing interest in our capabilities in this domain.

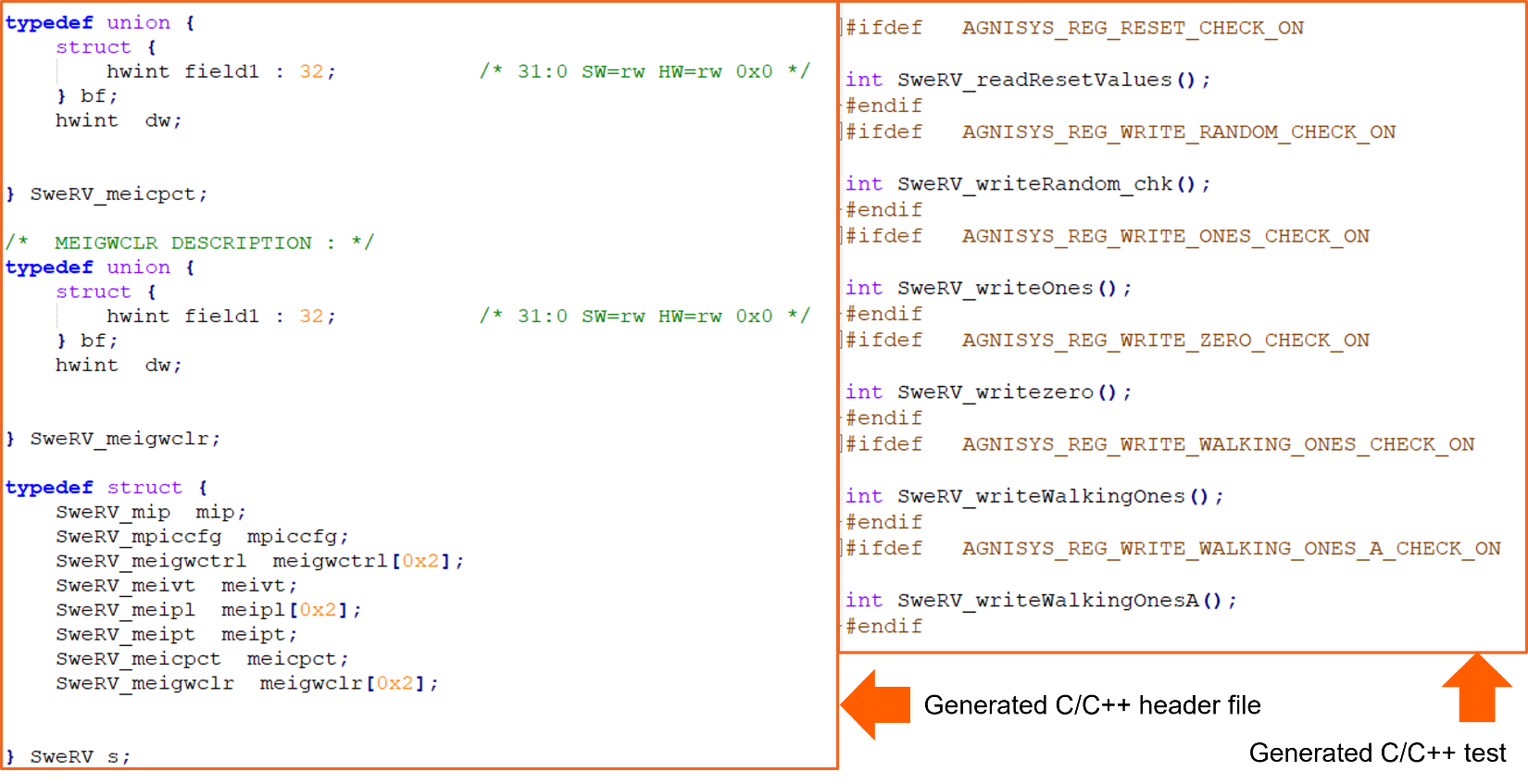

By embedded programming, I mean just about any type of software that interacts directly with the hardware. This includes boot code, firmware, device drivers, and what is sometimes called hardware-dependent software (HdS). In a system-on-chip (SoC) device, these programs generally run on the embedded processors within the chip, but some parts may run on a host system as well. The key common element is that the software controls and communicates with the hardware by reading and writing a set of control and status registers (CSRs). Because we support register automation, we can facilitate embedded code development by generating the C/C++ header files for the registers in the design.

Our IDesignSpec NextGen (IDS-NG) solution reads register definitions in a variety of popular formats and supports entry and modification of register details in an intuitive graphical editor. As shown in the diagram above, IDS-NG generates design code, verification code, and documentation in addition to the C/C++ code. The header files enable embedded programmers to get access to names, locations, and various properties of your registers and bit fields. Within IDS-NG, users can select from several options to suit their requirements:

- The header file contains structures and unions used to create an exact representation of the register model

- The header file contains macros and #define preprocessor commands but is devoid of any structures/unions for registers

- The header file conforms to MISRA C, a standard created by the Motor Industry Software Reliability Association

- The header file supports reuse at different levels/hierarchies of the register map with a base address argument for each block that is used multiple times

Having a ready-to-use C/C++ register description is obviously a great help, but programmers often would like additional support in writing the routines that access the registers. IDS-NG also generates C/C++ tests that check many aspects of the registers and memories within a design block. Reading and writing registers is just the start. The tests also check for proper operation of special register types such as alias, lock, shadow, FIFO, buffer, interrupt, counter, paged, virtual, external, and read/write pairs. Other generated tests include read/write of random values, zeroes and ones, and walking ones for both registers and memory.

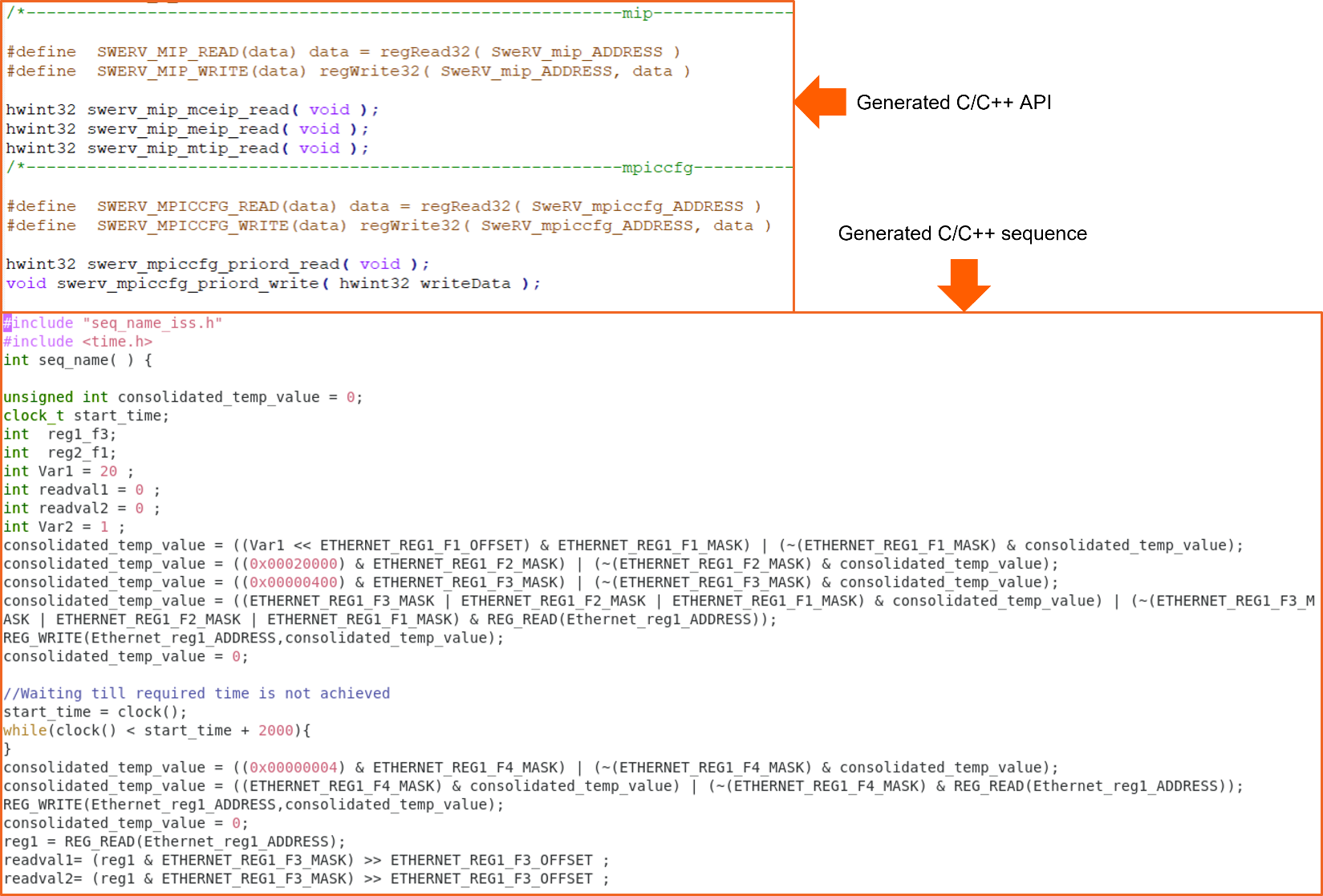

These tests are constructed using an application programming interface (API) that is also available to users for creating their own custom test sequences. IDS-NG enables users to describe the programming and test sequences of a device from a single specification and automatically generate sequences ready to use from the early stages of design and verification all the way to post-silicon validation. These sequences can be described naturally and succinctly in the same graphical editor used to define the registers and memories. Sequences can be simple, or complex involving conditional expressions, array of registers, loops, etc.

As noted earlier, hardware-dependent code can run on the processors within the chip or in a host system (for example, device drivers). In simulation, the same test sequences may be run from a testbench conforming to the Universal Verification Methodology (UVM). Further, these sequences are often adapted for use in automatic test equipment (ATE) during chip production. IDS-NG encompasses all these options, generating:

- The embedded processor C/C++ code, which may run in simulation but is essential for emulation, post-silicon validation in the bring-up lab, and chip operation in the field

- The SystemVerilog code necessary to run the sequences in the UVM testbench and to coordinate the processor-based tests with the UVM environment

- Various output files suitable for use by ATE engineers

In addition to supporting user-defined blocks with custom registers and sequences, we also provide our Standard Library of IP Generators (SLIP-G) for popular standard designs such as DMA, GPIO, I2C, I2S, PIC, SPI, AES, PWM, UART, and timers. Users have many options to customize these blocks, and IDS-NG tailors the registers and tests appropriately for their choices. We also make a standard configuration API available for each generated IP block so that programmers can easily supplement our tests with their own if they wish to do so.

To summarize, we do a lot to help embedded programmers. IDS-NG automatically generates C/C++ header files, tests, APIs, and sequences. Every time that you make a change in your specification, you can re-generate all these output files at the push of a button. This keeps all project teams in sync, reduces debug time, shortens your schedule, and saves resources. IDS-NG does the routine work of ensuring correctness with high quality, repeatable results, while your programmers focus on the algorithms and other differentiated parts of their code. To learn more, I invite you to watch our recorded webinar