The Ultimate Shift Left

Important observations from Einstein and New England’s ice traders..

Albert Einstein defined it well: “Insanity is doing the same thing over and over again and expecting different results.”

I have come across several semiconductor development teams, especially those in Fortune 500 companies, who do not have time to change their design process. They often cite various reasons such as:

- Too busy with the current project.

- What we have is working, so why change.

- Freeze in budget for new tool purchase.

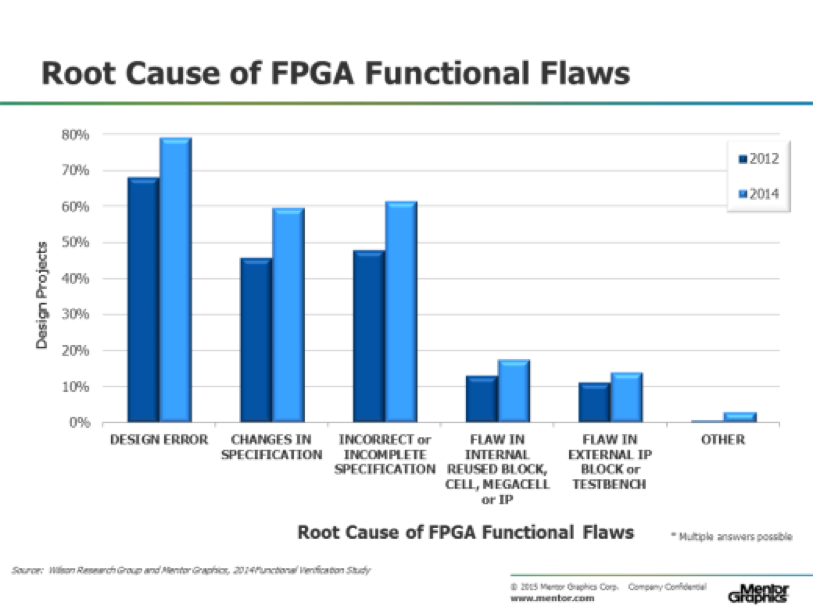

Yet, if you look at the flaws in the design process, as the recent study by Mentor Graphics shows, changes and incorrect or incomplete specification are the root cause of majority of functional flaws. I suspect that this issue is not just limited to FPGAs, but extends to IPs and SoCs, as well.

In order to avoid these mistakes, a better specification methodology is needed. I contend that using the specification as the driver and generating all the derived artifacts from it is the best way forward. This is the theme behind Agnisys’ products – IDesignSpec, IDS-Validate and IDS-Integrate.

There is always a desire to do things up front, as early on in the design process as possible. For example, do simulation before the lab debug, do timing analysis with RTL, do silicon validation before production. This “Shift Left” helps in identification of issues before more money is spent downstream.

A specification-centric and specification-driven development process is the ultimate Shift Left. Any more left will be in the engineer’s brain, because the process starts when a spec is created.

The SoC/IP design teams need to constantly spend time investigating new tools and methodologies, because who knows how many businesses have failed for lack of paying attention to emerging technology. This is like the ice traders of New England, who saw their business melt away once electric refrigerators came to market.