Using AI to Generate Chip Designs for AI Applications

Over the years, there have been some seismic shifts in the semiconductor industry. Because of the huge quantity used in computers, memory chips were the hot items for years. As the memory market commoditized, general-purpose processors (CPUs) became the big moneymakers. With the advent of graphic processing units (GPUs), the focus shifted to specialized processors. Most recently, chips for artificial intelligence (AI) applications have become the stars. This post considers how the design of such devices is putting pressure on the development process, and how AI itself can help.

AI Industry Evolution

Three years ago, I did an interview with Dan Nenni of SemiWiki in which we talked about how the rise of AI was changing the chip development process. It was timely since AI was starting to appear everywhere. Voice recognition and natural language processing (NLP) were required for many types of consumer devices, image recognition was gaining rapidly in importance, and talk of self-driving cars dominated the news media.

In the past three years, all forms of discussion about AI have been amplified. Many non-technical people have played with ChatGPT or similar applications and have formed strong opinions on their capabilities and potential. Terms such as machine learning (ML), deep learning (DL), and large language models (LLMs) are heard in everyday conversation. Some industry experts are wildly enthusiastic about the future of AI, while others worry that it might lead to the elimination of humanity.

The natural consequence of this evolution is much more attention on developing chips for use in AI applications. This is best exemplified by the meteoric rises in the revenue and stock value for AI chip pioneer NVIDIA. They are not alone; other established semiconductor vendors are investing heavily in AI, and a new generation of well-funded innovative startups has emerged. The unique demands of AI designs are leading to a corresponding evolution in chip development.

Developing AI Chips

Chips for AI applications are challenging to design, verify, and validate as part of the development process. One reason is that they are very large, which also puts pressure on implementation, test, and manufacturing. Other types of devices such as processors are also huge, but AI chips present some unique challenges. AI model layers, weights, operations, and functions are too variable to be implemented directly in fixed hardware.

AI flexibility requires customization of the data paths and processing logic, which can be accomplished by using architecturally-visible programmable registers commonly known as configuration and status registers (CSRs). The use of CSRs enables:

- Rearranging design elements as needed for the selected algorithms

- Scaling AI models and optimizing them for specific applications

- Trading off performance, power, and other design metrics

- Achieving unparalleled AI performance and efficiency

Achieving this flexibility requires powerful EDA solutions for register design, verification, and validation. These tools must support thousands of CSRs, including special types such indirect, indexed, read-only/write-only, alias, lock, shadow, interrupt, paged, virtual, external, read/write pairs, and many possible combinations. The EDA flow must help to develop the embedded software that configures and controls the registers in addition to the hardware implementation.

The Role of AI in EDA

Given that AI is affecting so many aspects of modern life, it is entirely reasonable to ask whether the EDA tools used in chip development might also benefit. In fact, EDA vendors started applying AI technologies such as ML and DL to back-end implementation functions such as layout several years ago. Learning from both previous chips and the current chip as it evolves yields deeper insight into the design and makes it easier to efficiently experiment with a wide range of “what if” scenarios.

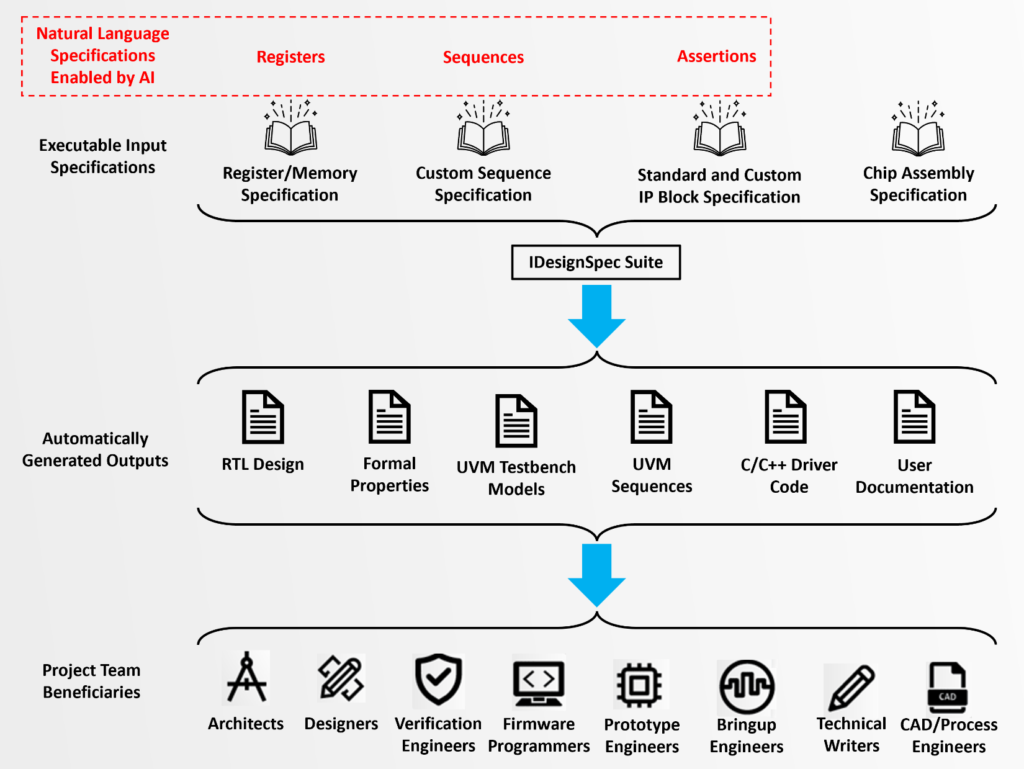

More recently, AI has been employed to improve the front-end aspects of the development flow as well. This approach has worked especially well in specification automation, the methodology of generating as many design, verification, and validation files as possible from executable golden specifications. This works extremely well for CSRs, although there are other areas of the design such as custom IP blocks and block interconnection where automation also adds great value.

AI has proven very helpful in enabling developers to use a wider range of specification formats, including natural language, as the input to the automation flow. CSR descriptions in standard formats such as IP-XACT and SystemRDL are not always readily available, so the ability to use existing documents saves considerable time and effort. While this is still an emerging technology, the nature of ML and LLMs means that AI-based specification automation is improving every single day.

The Agnisys Solution

At Agnisys, we have been applying AI to make our industry-leading IDesignSpec™ specification automation solution even better. Our most recent innovation is the ability to extract the information we need for CSR automation from PDF chip and IP datasheets. We are excited to make the SmartDatasheet site available now for all users, both our customer and other developers who want to take a look at our solutions.

SmartDatasheet uses leading-edge LLM technology to analyze datasheets, which include detailed CSR definitions so that programmers know how to access them when they write their embedded code. We generate structured output that is used by our IDesignSpec Suite to generate register-transfer-level (RTL) design files; Universal Verification Methodology verification models, tests, and testbenches; C/C++ headers and validation tests; IP-XACT and SystemRDL, and more. If the datasheet changes, users can regenerate updated files at the push of a button.

Making datasheets executable is not our only use of AI. We also apply NLP, ML, and DL to interpret custom CSR programming sequences specified in natural language so that IDesignSpec can convert them into UVM and C/C++ tests. We also provide the iSpec.ai site, where we use AI to process natural language descriptions of intended design behavior and generate SystemVerilog Assertions (SVA) automatically. Both SmartDatasheet and iSpec.ai are crowd-sourced so that the many examples submitted continually improve the ML-based results.

Summary

I’ve been as intrigued by the promise of AI as anyone, and have challenged our development team to apply appropriate techniques to our specification automation solutions. This is an ongoing process, but we are proud of the progress we’ve made. I invite you to follow the links in this post to learn more and to contact Agnisys if you have any questions or would like to see a demo.