Welcome Back to DAC – in Person – in San Francisco

Most engineers involved in the design, verification, and validation of electronic systems are familiar with the Design Automation Conference (DAC). It’s the stimulating combination of a highly technical conference with peer-reviewed papers and a lively trade show with a large exhibit floor. DAC is one of the highlights of the year for many silicon and software vendors, especially those of us in the electronic design automation (EDA) space. Sure, it’s a lot of work and expense to participate in DAC, but there’s no substitute for it in my experience.

Last year, for the first time in its 57-year history, DAC was a virtual event. Of course, the pandemic has resulted in many of our activities taking place online rather than in person, and for the most part we’ve adapted surprisingly well. Unfortunately, I can’t say that about the virtual trade shows in which we’ve participated. Frankly, the exhibit portions of last year’s DAC and most other online shows have been disappointing in terms of attendance at our “booths” or the level of interaction we were able to have with our users and potential users.

By the way, the technical portions of the conferences we’ve attended online, including DAC 2020, have gone very well. Our first AUGER user group meeting earlier this year was also virtual, and I was delighted by how smooth and natural it was. Maybe that’s not surprising; we’ve all been attending TED Talks and webinars for years. But there’s something different about trade shows. Without the ability to “kick the tires” and talk face to face, users seem reluctant to participate. I also suspect that online attendees get easily distracted by other work tasks and don’t have the same focus they have when walking a physical show floor, away from the office.

All these observations lead me to my main point: DAC is live again! The 58th edition of the show will be held at Moscone Center in San Francisco on December 6-8, with exhibit hours from 10 a.m. until 6 p.m. all three days. Agnisys will be there in Booth #2516 and we are really looking forward to seeing all of you there too. I’m personally thrilled to be able to travel again and to attend this show in person. Of course, we’ll be demonstrating all our products and chatting with design and verification engineers about their challenges and how we can help address them. But we’ll also be showing two valuable new additions to our specification automation solution.

I’m truly excited about our first foray into using artificial intelligence (AI) and machine learning (ML) for EDA applications. We’re big believers in the use of assertions for simulation and formal verification and, as I discussed in a recent post, we generate into SystemVerilog Assertions (SVA) from several types of specifications. We also encourage our users to write assertions for their custom logic, but we often receive feedback that the SVA syntax is complex and not easy to learn. So, we asked some of our engineers to think about generating other types of assertions from some sort of specification.

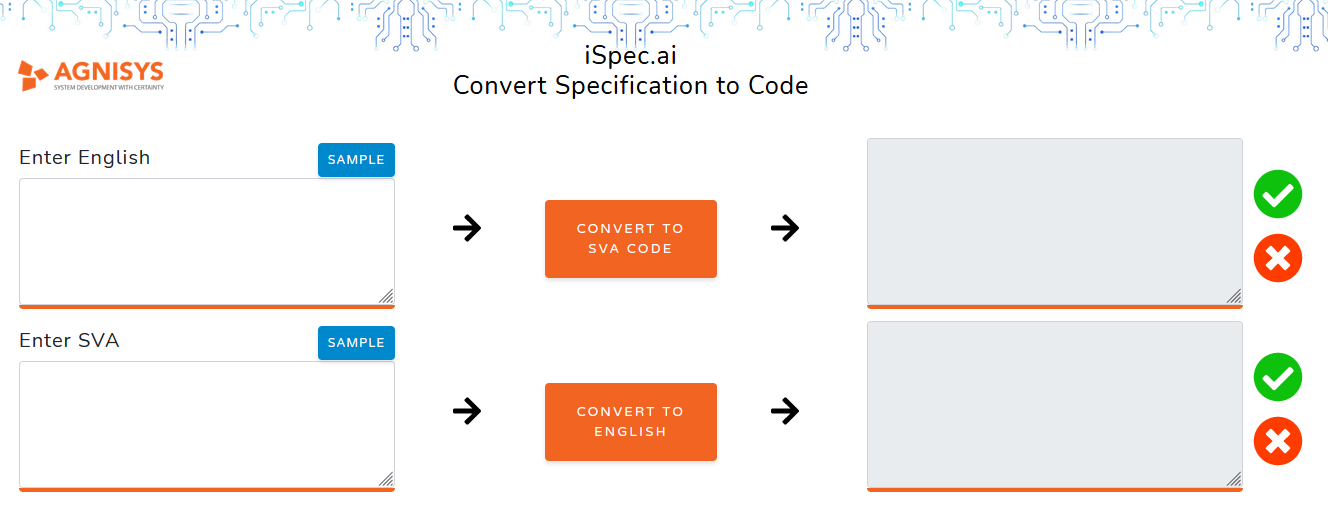

What they came up with is cool. They found that users naturally think about assertions in natural language, and so they created iSpec.ai, an AI/ML-powered technology that can translate English statements of design intent into SVA. ML applications learn by example and get better over time as more types of examples are provided. We fed iSpec.ai lots of assertions specified in English along with their SVA equivalents, with some help from industry experts. The results were impressive, but we were aware than there are many ways to specify design intent.

We took the novel approach of crowdsourcing to gather lots more examples. We invited our users to try their own assertion specifications on a website and to provide feedback on the quality of the SVA we generated. Our developers studied every one of these examples and used them to improve the technology. As we just announced, we have now opened the site to everyone. You can go to www.ispec.ai, submit some English descriptions, and use the SVA we generate. This is still an emerging technology, so you can just click a button to provide feedback on the results

iSpec.ai also generates English descriptions from SVA, which is very helpful in understanding assertions in IP blocks or code that you inherit from other sources. You can use this capability to add assertion descriptions to your verification plans or other documentation. I think that iSpec.ai has the potential to significantly increase the use of assertions without the need to learn all the details of SVA. More assertions will likely lead to wider adoption of formal verification. Assertions are equally valuable for ASIC and FPGA projects, which brings me our second innovation for this year’s DAC.

We’ve had customers using our products successfully for FPGA designs for years, but we received feedback that they would like better integration with their silicon vendor’s software tools. Our announcement includes the introduction of IDS-FPGA, a new member of our industry-leading IDesignSpec™ (IDS) family. We have integrated it with the Xilinx Vivado and Intel Quartus Prime software suites while providing a rich ready-to-use IP library for FPGA designs. You can cut your development time in half using our automated code generation and IP generators, and IDS-FPGA makes it even easier to add specification automation to your programmable device development flow.

I am eagerly inviting all of you to join us at DAC to see demonstrations of our latest technology and all our existing products. You will also have the opportunity to win valuable prizes by using iSpec.ai and answering quiz questions. More information is available at www.agnisys.com/events/design-automation-conference-dac-2021. See you in San Francisco!