Power Optimization by clock gating

Introduction

As smartphones and IoT devices proliferate, optimizing power usage is crucial in the design process. Today’s integrated circuits, packed with over 100 million transistors and operating at speeds beyond 1 GHz, consume significant power. IDS addresses this challenge with power optimization, employing clock gating techniques as a key solution.

How power optimization works

Let’s consider a simple example of a digital circuit to illustrate the importance of “power optimization”. We’ll look at a basic scenario involving a flip-flop and how power optimization techniques can impact its energy consumption.

Without Power Optimization:

Consider a flip-flop that toggles its output based on an input signal, and it is part of a larger digital system. The flip-flop transitions whenever there’s a change in the input signal

module NonOptimizedFlipFlop (input wire clk,input wire data,output reg q);always @(posedge clk) beginq <= data;endendmodule

In this non-optimized example, the flip-flop changes its output (q) on every rising edge of the clock (clk). This behavior can be power-consuming, especially if the input signal changes frequently.

With Power Optimization:

Now, let’s introduce a power optimization technique using clock gating. We’ll modify the design to include clock gating based on an enable signal.

module OptimizedFlipFlop (input wire clk,input wire data,input wire enable, // Enable signal for clock gatingoutput reg q);always @(posedge clk or enable) beginif (enable) beginq <= data;endendendmodule

In this optimized example, we’ve introduced an enable signal for clock gating. The flip-flop only updates its output when both the clock rises and the enable signal is asserted. This can significantly reduce power consumption when the input signal changes infrequently.

Explanation:

Non-Optimized Scenario:

- The flip-flop changes its output on every clock edge, regardless of whether the input signal changes. This consumes unnecessary power, especially if the input signal is stable for long periods.

Optimized Scenario:

- The flip-flop updates its output only when the enable signal is asserted. This allows the circuit to skip unnecessary transitions when the input signal remains constant, leading to power savings.

IDS support:

IDS supports the “clock_enable” property, allowing conditional register writes based on signals or access types. This property can be applied in three ways within IDS.

- Define a signal and assign it to the “clock_enable” property on the register (e.g., clock_enable=signal_name) for signal-dependent register writes.

- Set the property value to “true” for register writes dependent on the access type of the field. This gates HW and SW logic based on the register’s access.

- By introducing logic, IDS now supports two clocks i.e a gated clock and a regular clock (clk). Users have the flexibility to define their own logic or utilise default logic for the gated clock, which will be instantiated within the IDS block.

A typical design flow is visually depicted in the diagram below:

Example

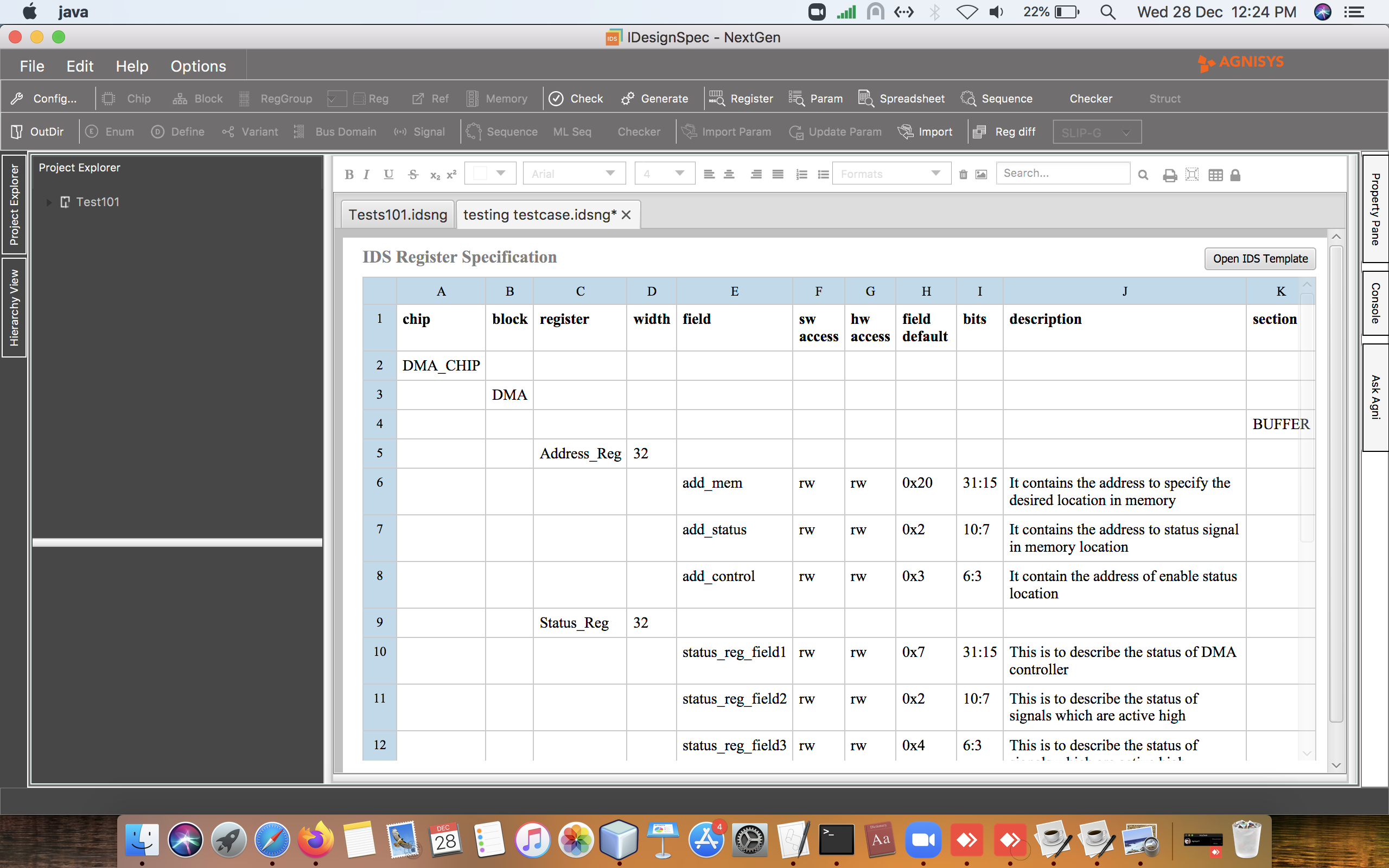

Let’s take a look at an example to understand this. Consider the following input

SystemRDL: property clock_enable {type = string ; component = addrmap|reg ; };

addrmap blk {

signal {}S1;

reg R1 {

clock_enable = "S1"; // First method by help of signal

field {

sw = rw;

hw = r;

}F0[31:0];

};

reg R2{

clock_enable = "true"; // Second method based on the register's access

regwidth = 16;

field {

hw = r;

sw = rw;

onread = rclr;

}F1[15:0];

};

R1 R1;

R2 R2;

};

Verilog output :

. . .

. . .

always @(posedge clk) begin

if (!reset_l)

begin

R1_F0_q <= 32'bx;

end

else

begin

if (S1)

begin

if (R1_wr_valid) //F0 : SW Write

begin

. . .

. . . .

always @(posedge clk) begin

if (!reset_l)

begin

R2_F1_q <= 16'bx;

end

else

begin

if(R2_rd_valid || R2_wr_valid)

begin if (R2_wr_valid) //F1 : SW Write

begin

. . . .

. . . .

By introducing logic: This constitutes the third method discussed earlier. With this approach, users have the flexibility to define their own logic or utilise default logic for the gated clock, which will be instantiated within the IDS block. The first argument of the property allows users to provide either their custom logic or default logic by defining a module in a separate file.

SystemRDL:

property clock_enable {type = string ; component = addrmap|reg ; };addrmap block {

clock_enable = "clk_gate1,test_en,gclk,default";

reg Reg1 {

field {

sw = rw;

hw = r;

}F1[31:0] = 31'h0;

};

Reg1 Reg1;

};

verilog output :

. . . .

. . . .

clk_gate1 clk_gate1_inst(

.clk(clk),

.ids_clk_en(ids_clk_en),

.gclk(gclk),

.test_en(test_en));

. . . .

. . . .

always @(posedge gclk) begin

if (!reset_l)

begin

Reg1_F1_q <= 32'd0;

end

else

begin

if (Reg1_wr_valid)

. . . .

. . . .

Importance of Optimization:

- Reduced Dynamic Power:

Clock gating reduces dynamic power consumption by preventing unnecessary switching activities when the flip-flop doesn’t need to change its state.

- Improved Energy Efficiency:

With clock gating, the flip-flop becomes more energy-efficient, making it suitable for battery-powered devices where energy conservation is crucial.

- Extended Battery Life:

In applications like mobile devices or IoT nodes, power optimization techniques contribute to longer battery life, enhancing the user experience.

Conclusion:

In conclusion, clock gating stands as a pivotal strategy in digital design, efficiently conserving energy, extending battery life, and aligning with sustainability goals while maintaining optimal functionality. It represents a commitment to achieving the delicate balance between performance and power efficiency in the dynamic landscape of modern VLSI circuit design.

PSS Support in IDS-Validate

Introduction

The Portable Test and Stimulus Standard defines a specification for creating a single representation of stimulus and test scenarios, usable by a variety of users across different levels of integration. With this standard, users can specify a set of behaviours, from which multiple implementations may be derived.

- PSS has constructs for

- Modelling Data flow (Buffers, Streams, States)

- Modeling Behavior (Actions, Activities, Components, Resource, Pooling)

- Constraints, Randomization, Coverage

- PSS is useful for SoC high-level test scenario creation

A concept of defining Registers and Sequences has been introduced in PSS2.0. Currently, three accesses are supported i.e., Read-Only, Read-Write, and Write-Only.

IDS-Validate helps in generating the PSS register model through various inputs supported by IDS such as SystemRDL, IP-XACT, IDS-NG, Word, Custom CSV, etc.

Steps for Generating PSS Register model using IDS-Validate

Use Case

IDS-Validate is a tool that helps verify the functionality of complex systems by creating and managing models of the hardware registers. These models regulate how the system interacts with the programmable registers in the hardware.

When testing a system, it’s important to ensure that the system reads from and writes to the hardware registers correctly. IDS-Validate uses the supported input from the system to generate a model called the PSS Register model. This model defines the rules for accessing the registers.

The PSS 2.0 LRM core library provides a set of tools and functions (APIs) to control how the system accesses the registers and allows for modelling of the registers. These tools help in creating and maintaining the PSS Register model.

One of the features of IDS-Validate is the generation of C code equivalents of PSS sequences. These C-based testbench environments can be used for various purposes like testing CPUs or checking embedded systems. This allows for more flexibility in testing and verification.

IDS-Validate also focuses on reusability and scalability. It enables efficient verification of complex systems by providing a model-based approach. The PSS Register model and the automated test generation make it easier to verify and test large systems. This scalability allows the tool to handle sophisticated verification tasks effectively.

Example

Input SystemRDL Register Specification:

addrmap block1{ reg reg1 {

field {

sw=rw;

hw=rw;

}f1=0;

};

reg reg2 {

field {

sw=rw;

hw=rw;

}f1=0;

field {

sw=rw;

hw=rw;

}f2[31:15]=0;

};

reg reg3 {

field {

sw=rw;

hw=rw;

}f1[31:0]=32'h10;

};

reg1 reg1;

reg2 reg2;

reg3 reg3;

};

PSS Sequence specification for the Register model defined above in SystemRDL format:

/* Package containing block1 HW registers as PSS register components*/package block1_regs_pkg {

import addr_reg_pkg::*;

struct reg1_reg_s : packed_s<> {

bit[1] f1;

bit[31] rsvd_0;

};

struct reg2_reg_s : packed_s<> {

bit[1] f1;

bit[14] rsvd_0;

bit[17] f2;

};

struct reg3_reg_s : packed_s<> {

bit[32] f1;

};

component block1_regs_c: reg_group_c {

reg_c<reg1_reg_s,READWRITE,32> reg1

exec init {

reg1.offset = 0x0;

reg1.reset_val = 0x00000000;

reg1.reset_mask = 0x1;

};

reg_c<reg2_reg_s,READWRITE,32> reg2

exec init {

reg2.offset = 0x4;

reg2.reset_val = 0x00000000;

reg2.reset_mask = ;

};

reg_c<reg3_reg_s,READWRITE,32> reg3

exec init {

reg3.offset = 0x8;

reg3.reset_val = 0x00000010;

reg3.reset_mask = 0xFFFFFFFF;

};

}

};

Steps for Generating Firmware and UVM sequence Output using IDS-Validate.

Sequences are a “set of steps” that involve writing/reading specific bit fields of the registers in the IP/SoC. These sequences can be simple, or complex involving conditional expressions, an array of registers, loops, etc. PSS users can write a single sequence specification and a compiler has been written to generate the UVM sequences for verification, System Verilog sequences for validation, C code for firmware and device driver development, and various output formats for Automatic Test Equipment.

This provides a solution for firmware engineers to write and debug their device drivers and application software. Consequently, PSS helps in the solution for SOC/IP teams who aim to cut down the verification and validation time, through automatic generation of UVM and sequences which enables exhaustive testing of memories and register maps.

This approach also unifies the creation of portable sequences from a golden specification. Sequences can be captured in PSS, python, spreadsheet format, or GUI(NG) and generate multiple output formats for a variety of domains:

- UVM sequences for verification

- SystemVerilog sequences for validation

- C code for firmware and device driver development

- Specialized formats for automated test equipment (ATE)

- Hooks to the latest Portable Stimulus Standard (PSS)

- Documentation outputs such as HTML and flowchart

The sequence constructs include loops, if-else, wait, and switch statements to change the interfaces, specify encoding formats, deal with time-unit differences, use macros, specify variants, and use return statements to return user errors from sequences. The constructs support constrained variables for randomized sequences and handling of indirect and interrupt registers.

Example

Input PSS sequence Specification:

Example

- Input PSS Sequences

- Generated Firmware Sequences

- Generated UVM sequences

Steps to Start Using

If you already have IDS, get a licence for IDS-Validate. The command to use is Agnisys PSS Compiler or apc.sh and you can generate several outputs from it.

% apc.sh <input file> -out “<desired_output>” -dir <output dir> -illegalbins

APC(AGNISYS PSS COMPILER/EDITOR)

We are excited to introduce the latest update to our software, which includes the integration of a dedicated PSS (Portable Stimulus and Test Language) Editor. This new addition enables you to work with PSS files, create and edit portable stimulus models and tests with ease and ensures a seamless experience for engineers and testers working with this industry-standard language.

Key Features:

- PSS File Management: The PSS Editor allows you to efficiently manage your Portable Stimulus and Test Language files. Create new PSS files, open existing ones, and organize your project resources in a user-friendly interface.

- Syntax Highlighting: Enjoy syntax highlighting and code formatting that makes writing and reviewing PSS code more intuitive and error-resistant.

- Code Navigation: Easily navigate through complex PSS files with features like code folding, context-aware code suggestions, and jump-to-definition functionality.

- Validation and Semantic checks:: Utilize built-in validation and debugging tools to ensure your PSS models and tests adhere to industry standards and functional requirements..

- Search and Replace: Quickly find and replace elements within your PSS code, improving code maintenance and efficiency.

If you wish to install and use the tool, download and install it directly from the Visual Studio Code (VS Code) Marketplace and Follows the instruction given in README.md

https://marketplace.visualstudio.com/items?itemName=AgnisysInc.agnisysPSS

Conclusion

IDS-Validate is a powerful tool that simplifies the verification of complex systems by creating and managing models of hardware registers. Generating the PSS Register model based on the system’s input ensures correct interaction with the programmable registers. With the support of the PSS 2.0 LRM core library, the tool provides tools and functions for modelling and controlling register access. By automating test generation and facilitating reuse, IDS-Validate saves time and effort in system verification. The ability to generate C code equivalents of PSS sequences adds flexibility to the testing process. Overall, IDS-Validate enhances reusability and scalability, making it an effective solution for the verification of sophisticated system-level designs.PSS compiler and GUI generator have been developed for the generation of various outputs from the above golden custom sequence specification such as:

- SystemVerilog/MATLAB output for Validation

- UVM output for Verification

- C output for Firmware

- CSV output for ATE

- HTML/Flowchart for documentation

PSS editor enables you to work with PSS files, create and edit portable stimulus models and tests with ease, and ensures a seamless experience for engineers and testers working with this industry-standard language.

Flowchart Output

Introduction

Flowcharts are widely used in multiple fields to document, study, plan, improve and communicate often complex processes in clear, easy-to-understand diagrams. It uses rectangles, ovals, diamonds and potentially numerous other shapes to define the type of steps, along with connecting arrows to define flow and sequence.

Usage

IDS-Validate offers a convenient method for generating FlowchartGraph Output. This is achieved by employing the iss_graph option in the IDSBatch command line. The syntax for utilising this feature is as follows:

To use this feature, the iss_graph option is used in the output command.

Syntax: idsbatch <filename> -out “iss_graph” -dir <output dir_name/path>

Example: idsbatch sample1 -out iss_graph -dir ids

Executing the above command results in the creation of an iss_graph.htm file with the input file name in the specified directory (ids in this case). This file can be easily opened using any web browser.

Functionality

One of the key features of the Flowchart output is its visually appealing specification with dynamic elements. It effectively captures and represents the intricate details of loops and statements within the flowchart.

This flowchart will support all the statements, loops, conditional operators like for, while, if, else, else if, go to, break.

Example

Output

Conclusion

The Flowchart Output is a powerful tool for visualizing and comprehending complex processes through dynamic flowcharts. Its ease of use within the IDS-Validate product makes it a valuable asset for professionals across various fields.