IDS-BatchTM CLI Command-Line Next Generation Semiconductor Specification Automation

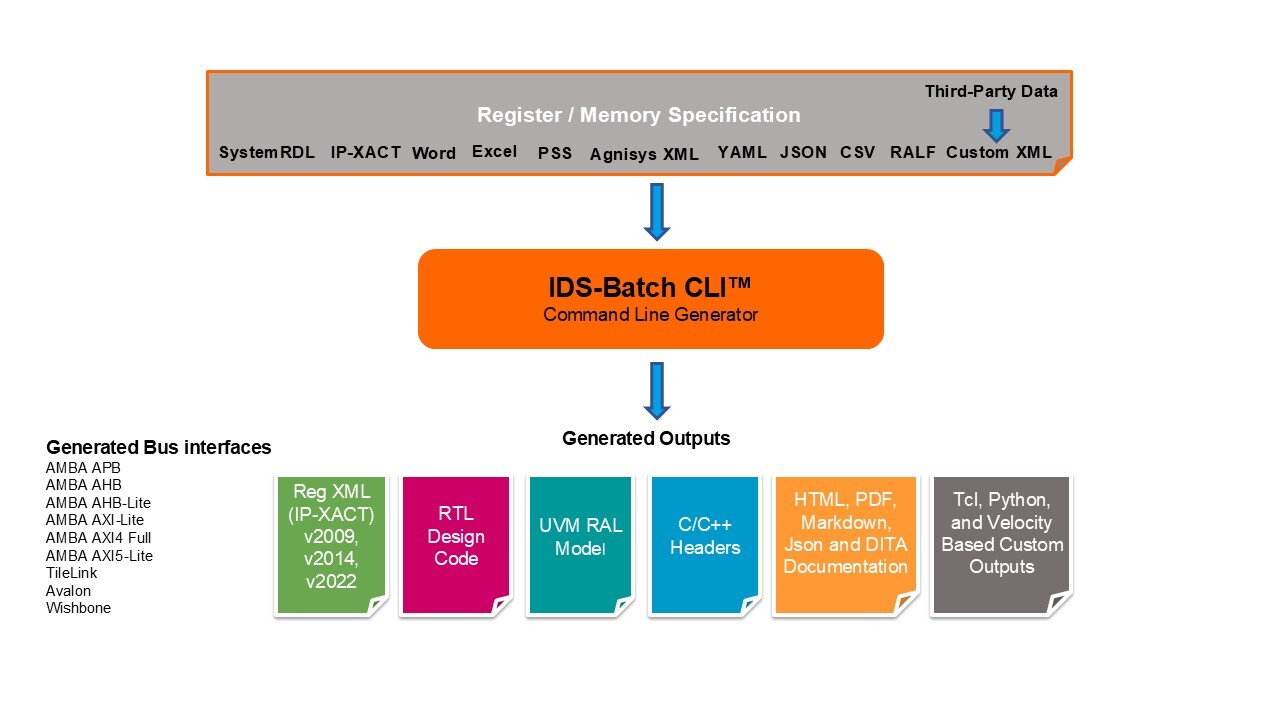

The Agnisys IDesignSpec™ (IDS) Suite provides a complete solution for executable hierarchical specification of the memories, register sets, registers, and register fields in your IP or SoC. You can import existing descriptions in standard formats such as SystemRDL, IP-XACT, JSON, RALF, YAML, XML, and comma-separated values (CSV) files for generation of various RTL, UVM, C/C++ Header, documentation collartals.

Powerful Register and Memory Editor with SystemVerilog & UVM Generation

IDS-Batch CLI fits seamlessly into your SoC or IP development flow, including integration with the Git revision control system to manage both text and graphics files while fostering collaboration.

How IDS-Batch CLI Enhances Your Development Process

Your executable specifications are read by IDS-Batch CLI, supporting the use of simple registers and more than 400 special register types, including indirect, indexed, alias, lock, shadow, FIFO, trigger buffer, interrupt, counter, paged, virtual, external, read/write pairs, accumulate and combinations of these types.

.

Automatic generation of files for design, verification, software development, and documentation

From your specifications, IDS-Batch CLI generates output files for your design, verification, software, and documentation teams. It generates the complete RTL description for your registers and memories, including a bus slave and decode logic specific to your selected bus protocol and any clock-domain-crossing (CDC) synchronization logic needed. This enables instant connection of your design to the register bus. Support interfaces include APB, AHB, AHB-Lite, AXI4, AXI5-Lite, TileLink, Avalon, Wishbone, and proprietary buses.

Generation of SystemVerilog, Verilog, VHDL, or SystemC RTL code

IDS-Batch CLI generates a SystemVerilog model compatible with the UVM standard and suitable for inclusion in your UVM testbench. This eliminates a lot of work on the part of your designers and verification team. IDS-Batch CLI helps your embedded programmers as well, by generating C/C++ headers for the memories, registers, and fields. This replaces tedious manual transcription of specification details into code and avoids any chance of errors in the process.

Automatically generated documentation for registers and memories

Download the IDesignSpec Suite Brochure

Benefits of IDS-Batch CLI

The automatic generation of all these files for the project teams saves time and resources early in the project. Every file generated by IDS-Batch CLI is one that you do not have to code by hand. The correct-by-construction nature of specification generation also eliminates entire categories of bugs, accelerating verification and pre-silicon validation. IDS-Batch CLI provides even more value every time that a specification changes. You simply run it to re-generate all relevant files. The key benefits are:

- Eliminates manual update effort and ensures that all your teams are always in sync

- Easy integration into your makefiles or check-in scripts for revision control systems

- Easy integration into your continuous integration/continuous development (CI/CD) flows

- Whenever a specification changes, IDS-Batch CLI can be run automatically on the command line and generate the updated files

- All other Agnisys products also generate their outputs in command-line mode using IDS-Batch CLI

What Our Clients Say