SystemRDL

Contemporary system-on-chip (SoC) designs are essential for all the most demanding electronics applications: artificial intelligence (AI), high-performance computing (HPC), autonomous vehicles, smartphones, and more. Many different architectures, processors, bus protocols, and intellectual property (IP) blocks are available to support these diverse chips. However, one key design component spans all applications: programmable registers, which can be specified using the System Register Description Language (SystemRDL) standard.

Registers Are Everywhere

The Role of SystemRDL

SystemRDL Overview

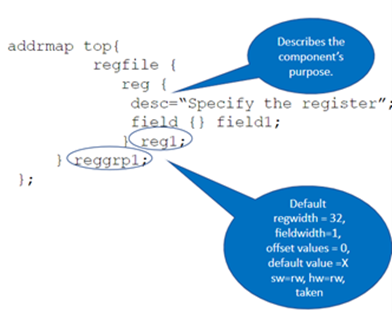

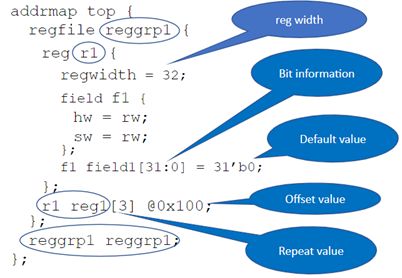

Designers or architects use SystemRDL to describe registers (and memories) along with their properties in a concise format that is readable by both humans and EDA tools. Attributes of each register can include width, fields within the register, and number of bits in each field. There are two forms of register definition: anonymous and definitive. In the latter case, a register can be defined once and then instantiated multiple times within the SystemRDL specification.

Example of an Anonymous Definition

Agnisys SystemRDL Compiler

Agnisys SystemRDL Editor

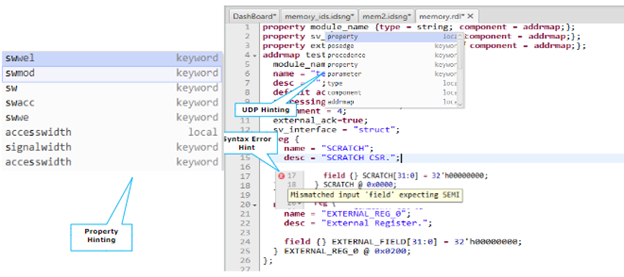

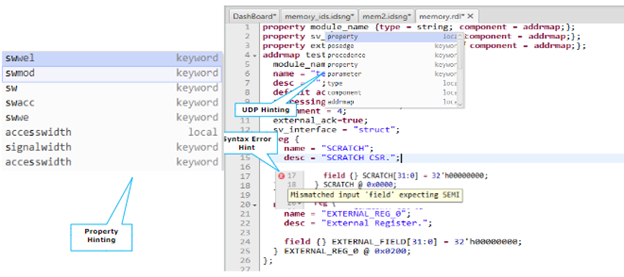

In addition to the semantic and syntax checks for SystemRDL specifications, Agnisys offers a specialized text editor to make it much easier to write them efficiently and correctly. Key features include:

- Essential functions such as copy, paste, select all, and find

- Automatic indentation for better readability and maintenance

- Keyword and syntax highlighting to aid in understanding components

- Intelligent, context-specific SystemRDL property hinting (suggestions)

- Template hinting and insertion with or without parameters

- Highlighting of SystemRDL syntax errors.

- Full support for parameter overriding, dynamic assignment, and stride syntax

- Code folding so that long and complex code segments can be collapsed or expanded

- Support for all UDP properties, with usage description and documentation links

Summary

Programmable registers are essential for the configuration and operation of SoC designs. The SystemRDL standard is one way to specify these registers in a clear and unambiguous way. With its SystemRDL Compiler, Agnisys fully supports this standard. The IDesignSpec Suite supports an unparalleled range of special register types and automatically generates all the register-related files required for design, programming, verification, validation, and documentation. This saves an enormous amount of time and resources many times over the course of an IP or SoC project. Click here to view visual studio marketplace