IDS-VerifyTM

Test and Testbench Specification Automation

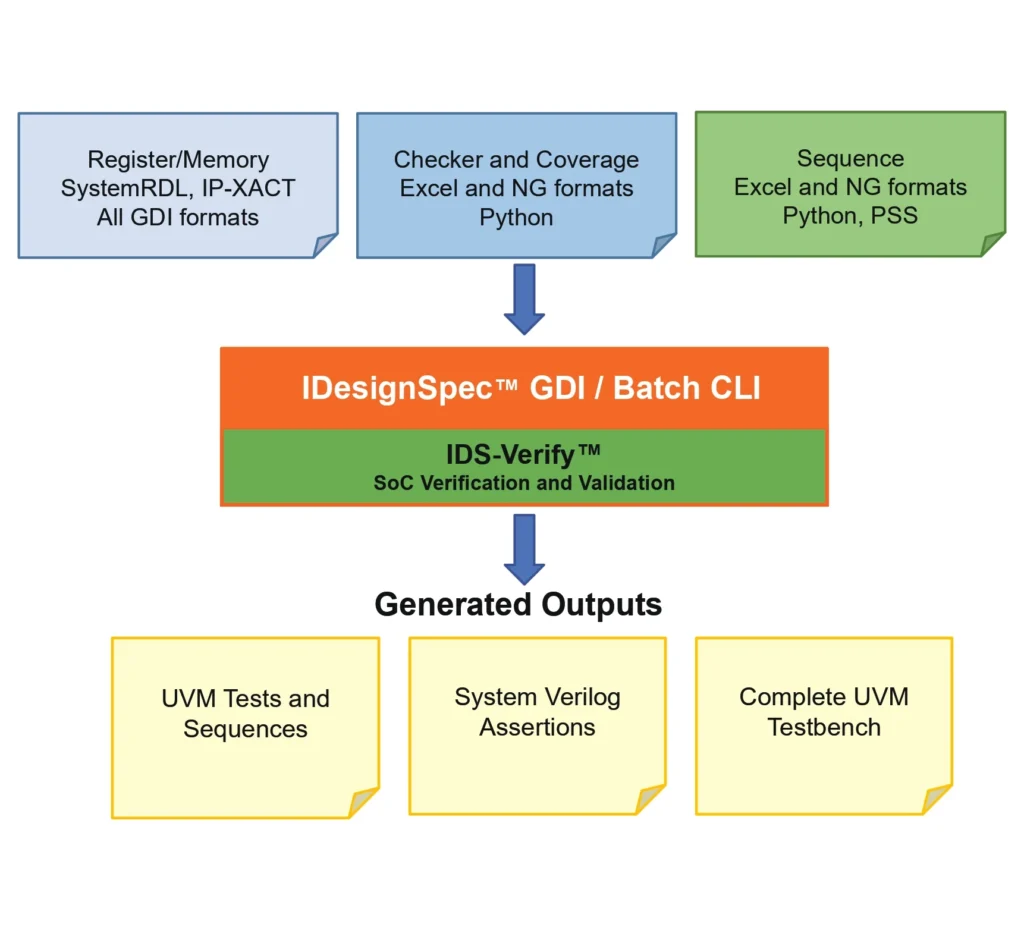

The UVM models and C/C++ headers generated by IDesignSpec GDI and IDS-Batch CLI define the register interface through which software monitors and controls the hardware design. Your verification engineers must obtains or develop the UVM sequences necessary to configure, program, and test the registers and memories in the design. Embedded programmers must obtain or write the C/C++ code to perform similar functions for system validation and for production use of the SoC or IP block in the field.

Continuous Alignment Between the Specification and Tests and Testbench Code

If your verification and software teams manually write sequences in their respective formats, they waste time and resources. There is a high likelihood of differing interpretations and the challenge of keeping the two teams in sync every time the specification changes.

Fortunately, Agnisys has IDS-Verify, a specification solution for automatic register test, custom register-based sequences, and testbenches in simulation as well as formal verification of registers.

Fortunately, Agnisys has IDS-Verify, a specification solution for automatic register test, custom register-based sequences, and testbenches in simulation as well as formal verification of registers.

How IDS-Verify Enhances Your Development Process

IDS-Verify enables you to describe the custom configuration, programming, and test sequences of your design and automatically generate sequences ready to use during your RTL simulation. From a single sequence specification, IDS-Verify generates UVM sequences for verification and associated documentation. You specify the sequences using a rich language and command feature set that includes loops, branch, wait, calls, switch, and macros.

.

Syntax and semantics checker and debugger

IDS-Verify includes a sophisticated syntax and semantics checker for the sequence descriptions to catch common user errors. The entire sequence specification is validated and a report containing a complete list of all problems opens in a window for viewing with cross-navigation to the specification row containing the problem.

Automatic generation of testbenches for verification

The generated UVM models and UVM sequences can easily be incorporated into your existing SoC or IP UVM-based testbenches. However, IDS-Verify also supports the ability to automatically generate a complete testbench-based verification environment and tests for automatically verifying all your addressable registers and memories with all access types and all complex types for IP and SoC designs.

The generated testbench is fully compliant with UVM, including bus agents, monitors, drivers, adaptors, predictors, and sequences, as well as Makefiles for common simulators. The UVM testbench is connected to the UVM register model and RTL design generated by IDesignSpec GDI, providing pushbutton verification.

The generated testbench is fully compliant with UVM, including bus agents, monitors, drivers, adaptors, predictors, and sequences, as well as Makefiles for common simulators. The UVM testbench is connected to the UVM register model and RTL design generated by IDesignSpec GDI, providing pushbutton verification.

Automatic generation of sequences

IDS-Verify automatically generates different sequences for the many types of registers supported by IDesignSpec GDI. including sequences for register fields, register-level sequences, and positive/negative sequences for special register types.

The generated UVM testbench can include sequences, configuration, checkers, coverage, assertions, and inter-component “plumbing” for your design in addition to memories and registers.

The generated UVM testbench can include sequences, configuration, checkers, coverage, assertions, and inter-component “plumbing” for your design in addition to memories and registers.

Automatic generation of assertions

IDS-Verify automatically generates SystemVerilog Assertions (SVA) for use in both simulation and formal verification.

Download the IDesignSpec Suite Brochure

View a summary of each product and how the suite enables your semiconductor teams to more rapidly develop products while improving efficiency.